- 您现在的位置:买卖IC网 > PDF目录363350 > NM24W16UFLZVN (FAIRCHILD SEMICONDUCTOR CORP) 16K-Bit Serial EEPROM 2-Wire Bus Interface PDF资料下载

参数资料

| 型号: | NM24W16UFLZVN |

| 厂商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分类: | PROM |

| 英文描述: | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| 中文描述: | 2K X 8 I2C/2-WIRE SERIAL EEPROM, PDIP8 |

| 封装: | PLASTIC, DIP-8 |

| 文件页数: | 7/13页 |

| 文件大小: | 109K |

| 代理商: | NM24W16UFLZVN |

7

www.fairchildsemi.com

NM24C16U/17U Rev. B.1

N

Device Operation

Background Information (IIC Bus)

As mentioned, the IIC bus allows synchronous bidirectional com-

munication between Transmitter/Receiver using the SCL (clock)

and SDA (Data I/O) lines. All communication must be started with

a valid START condition, concluded with a STOP condition and

acknowledged by the Receiver with an ACKNOWLEDGE condi-

tion.

As shown below, the EEPROMs on the IIC bus may be configured

in any manner required, the total memory addressed can not

exceed 16K (16,384 bits). EEPROM memory address program-

ming is controlled by 2 methods:

All unused pins must be grounded

(tied to V

SS

).

Software addressing the required PAGE BLOCK within the

device memory array (as sent in the Slave Address string).

For devices with densities greater than 16K, a different protocol,

the Extended IIC protocol, is used. Refer to NM24C32U datasheet

(for example) for additional details.

Addressing an EEPROM memory location involves sending a

command

string

with

the

[DEVICE TYPE]

–

[DEVICE ADDRESS]

–

[PAGE BLOCK AD-

DRESS]

–

[BYTE ADDRESS]

following

information:

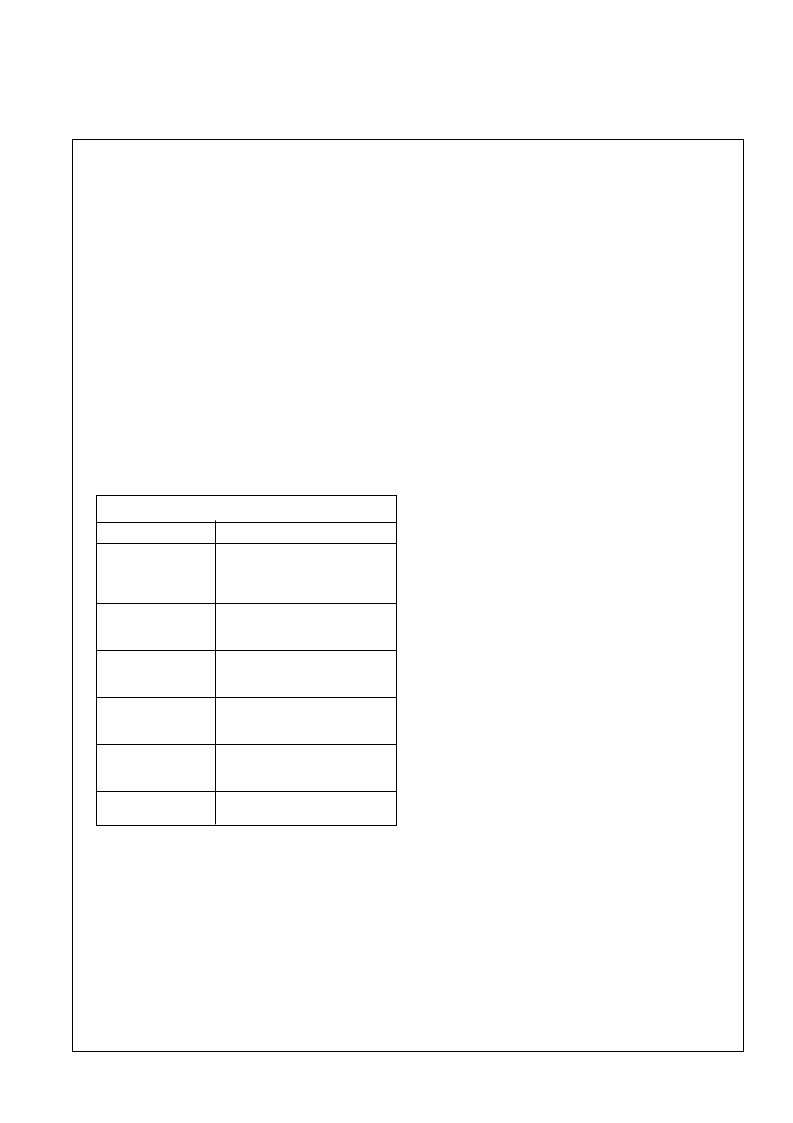

DEFINITIONS

WORD

8 bits (byte) of data

PAGE

16 sequential addresses (one byte

each) that may be programmed

during a 'Page Write' programming

cycle

PAGE BLOCK

2048 (2K) bits organized into

16

pages of addressable memory.

(8 bits) x (16 pages) = 2048 bits

MASTER

Any IIC device CONTROLLING the

transfer of data (such as a

microprocessor)

SLAVE

Device being controlled

(EEPROMs are always considered

Slaves)

TRANSMITTER

Device currently SENDING data on

the bus (may be either a Master or

Slave).

RECEIVER

Device currently RECEIVING data

on the bus (Master or Slave)

Pin Descriptions

Serial Clock (SCL)

The SCL input is used to clock all data into and out of the device.

Serial Data (SDA)

SDA is a bidirectional pin used to transfer data into and out of the

device. It is an open drain output and may be wire

–

ORed with any

number of open drain or open collector outputs.

WP Write Protection (NM24C17U Only)

If tied to V

CC

, PROGRAM operations onto the upper half of the

memory will not be executed. READ operations are possible. If

tied to V

SS

, normal operation is enabled, READ/WRITE over the

entire memory is possible.

This feature allows the user to assign the upper half of the memory

as ROM which can be protected against accidental programming.

When write is disabled, slave address and word address will be

acknowledged but data will not be acknowledged.

Device Operation

The NM24C16U/17U supports a bidirectional bus oriented proto-

col. The protocol defines any device that sends data onto the bus

as a transmitter and the receiving device as the receiver. The

device controlling the transfer is the master and the device that is

controlled is the slave. The master will always initiate data

transfers and provide the clock for both transmit and receive

operations. Therefore, the NM24C16U/17U will be considered a

slave in all applications.

Clock and Data Conventions

Data states on the SDA line can change only during SCL LOW.

SDA state changes during SCL HIGH are reserved for indicating

start and stop conditions. Refer to Figure 2 and Figure 3 on next

page.

Start Condition

All commands are preceded by the start condition, which is a

HIGH to LOW transition of SDA when SCL is HIGH. The

NM24C16U/17U continuously monitors the SDA and SCL lines for

the start condition and will not respond to any command until this

condition has been met.

Stop Condition

All communications are terminated by a stop condition, which is a

LOW to HIGH transition of SDA when SCL is HIGH. The stop

condition is also used by the NM24C16U/17U to place the device

in the standby power mode.

Write Cycle Timing

Acknowledge

Acknowledge is a hardware convention used to indicate success-

ful data transfers. The transmitting device, either master or slave,

will release the bus after transmitting eight bits.

During the ninth clock cycle the receiver will pull the SDA line to

LOW to acknowledge that it received the eight bits of data. Refer

to Figure 4.

相关PDF资料 |

PDF描述 |

|---|---|

| NM24W16UFTMT8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTN | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVM8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVMT8 | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

| NM24W16UFTVN | 16K-Bit Serial EEPROM 2-Wire Bus Interface |

相关代理商/技术参数 |

参数描述 |

|---|---|

| NM-250 | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM-250-0015P | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM-250-0025P | 制造商:WALDOM ELECTRONICS 功能描述: |

| NM25001S00 | 制造商:RadiSys 功能描述:LVDS;ADDCARD;BG845&LS855 |

| NM25C020 | 制造商:FAIRCHILD 制造商全称:Fairchild Semiconductor 功能描述:2K-Bit Serial CMOS EEPROM (Serial Peripheral Interface (SPI) Synchronous Bus) |

发布紧急采购,3分钟左右您将得到回复。