- 您现在的位置:买卖IC网 > PDF目录189437 > OR2T26A-6S352I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | OR2T26A-6S352I |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 128/192页 |

| 文件大小: | 3148K |

| 代理商: | OR2T26A-6S352I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页当前第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页

40

Lucent Technologies Inc.

Data Sheet

ORCA Series 2 FPGAs

June 1999

FPGA States of Operation

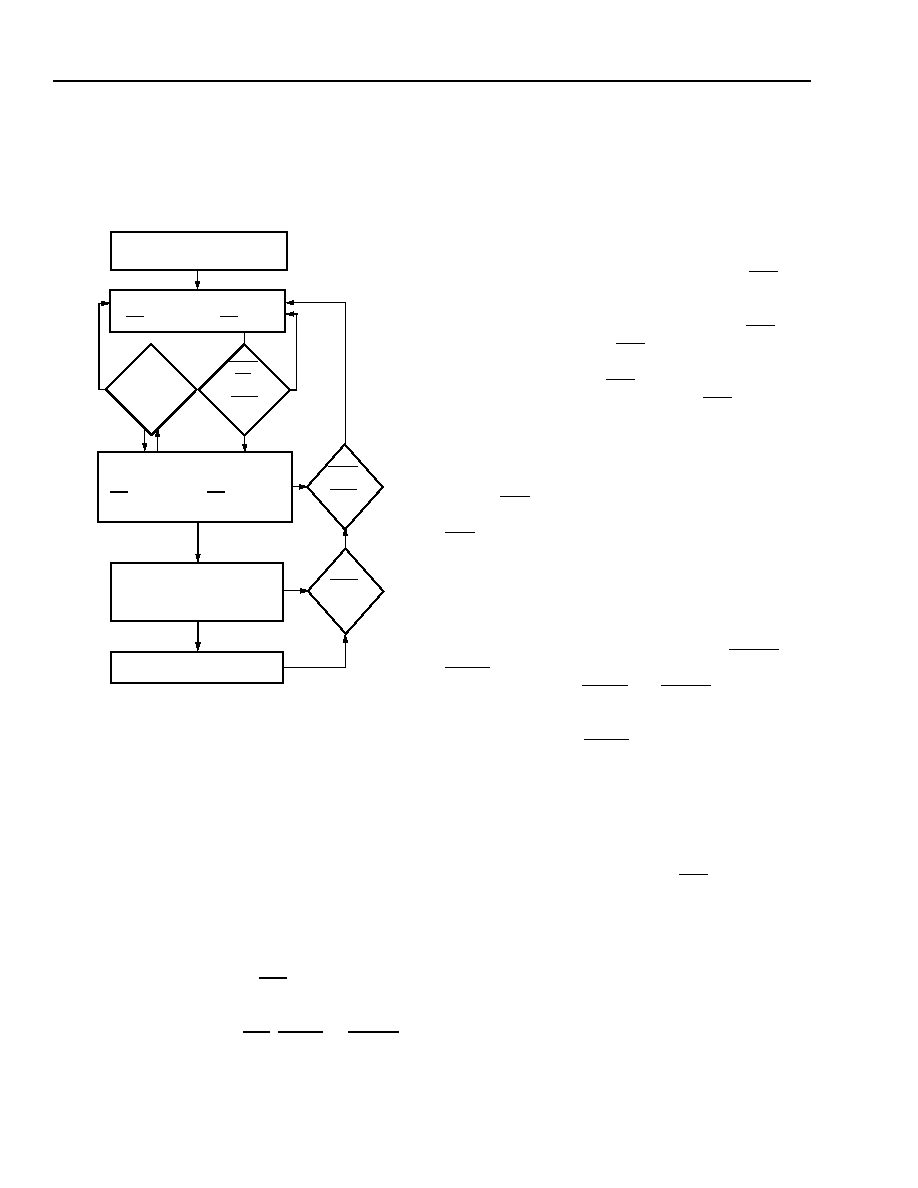

Prior to becoming operational, the FPGA goes through a

sequence of states, including initialization, configuration,

and start-up. Figure 36 outlines these three FPGA

states.

5-4529(F).r6

Figure 36. FPGA States of Operation

Initialization

Upon powerup, the device goes through an initialization

process. First, an internal power-on-reset circuit is trig-

gered when power is applied. When VDD reaches the

voltage at which portions of the FPGA begin to operate

(2.5 V to 3 V for the OR2CxxA, 2.2 V to 2.7 V for the

OR2TxxA/OR2TxxB), the I/Os are configured based on

the configuration mode, as determined by the mode

select inputs M[2:0]. A time-out delay is initiated when

VDD reaches between 3.0 V and 4.0 V (OR2CxxA) or

2.7 V to 3.0 V (OR2TxxA/2TxxB) to allow the power

supply voltage to stabilize. The INIT and DONE outputs

are low. At powerup, if VDD does not rise from 2.0 V to

VDD in less than 25 ms, the user should delay configu-

ration by inputting a low into INIT, PRGM, or RESET

until VDD is greater than the recommended minimum

operating voltage (4.75 V for OR2CxxA commercial

devices and 3.0 V for OR2TxxA/B devices).

At the end of initialization, the default configuration

option is that the configuration RAM is written to a low

state. This prevents shorts prior to configuration. As a

configuration option, after the first configuration (i.e., at

reconfiguration), the user can reconfigure without

clearing the internal configuration RAM first.

The active-low, open-drain initialization signal INIT is

released and must be pulled high by an external resis-

tor when initialization is complete. To synchronize the

configuration of multiple FPGAs, one or more INIT pins

should be wire-ANDed. If INIT is held low by one or

more FPGAs or an external device, the FPGA remains

in the initialization state. INIT can be used to signal that

the FPGAs are not yet initialized. After INIT goes high

for two internal clock cycles, the mode lines (M[3:0])

are sampled and the FPGA enters the configuration

state.

The high during configuration (HDC), low during config-

uration (LDC), and DONE signals are active outputs in

the FPGA’s initialization and configuration states. HDC,

LDC, and DONE can be used to provide control of

external logic signals such as reset, bus enable, or

PROM enable during configuration. For parallel master

configuration modes, these signals provide PROM

enable control and allow the data pins to be shared

with user logic signals.

If configuration has begun, an assertion of RESET or

PRGM initiates an abort, returning the FPGA to the ini-

tialization state. The PRGM and RESET pins must be

pulled back high before the FPGA will enter the config-

uration state. During the start-up and operating states,

only the assertion of PRGM causes a reconfiguration.

In the master configuration modes, the FPGA is the

source of configuration clock (CCLK). In this mode, the

initialization state is extended to ensure that, in daisy-

chain operation, all daisy-chained slave devices are

ready. Independent of differences in clock rates, master

mode devices remain in the initialization state an addi-

tional six internal clock cycles after INIT goes high.

When configuration is initiated, a counter in the FPGA

is set to 0 and begins to count configuration clock

cycles applied to the FPGA. As each configuration data

frame is supplied to the FPGA, it is internally assem-

bled into data words. Each data word is loaded into the

internal configuration memory. The configuration load-

ing process is complete when the internal length count

equals the loaded length count in the length count field,

and the required end of configuration frame is written.

– ACTIVE I/O

– RELEASE INTERNAL RESET

– DONE GOES HIGH

START-UP

INITIALIZATION

CONFIGURATION

RESET

OR

PRGM

LOW

PRGM

LOW

– CLEAR CONFIGURATION MEMORY

– INIT LOW, HDC HIGH, LDC LOW

OPERATION

POWERUP

– POWER-ON TIME DELAY

– M[3:0] MODE IS SELECTED

– CONFIGURATION DATA FRAME WRITTEN

– INIT HIGH, HDC HIGH, LDC LOW

– DOUT ACTIVE

YES

NO

RESET,

INIT,

OR

PRGM

LOW

BIT

ERROR

YES

相关PDF资料 |

PDF描述 |

|---|---|

| OR2T26A-6S432 | Field-Programmable Gate Arrays |

| OR2T26A-6S432I | Field-Programmable Gate Arrays |

| OR2T26A-6T208 | Field-Programmable Gate Arrays |

| OR2T26A-6T208I | Field-Programmable Gate Arrays |

| OR2T26A-6T240 | Field-Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR2T26A7BA352-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7BC432-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7PS208-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7PS240-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7S208-DB | 功能描述:FPGA - 现场可编程门阵列 Use LatticeEC RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。