- 您现在的位置:买卖IC网 > PDF目录189437 > OR2T26A-6S352I (Electronic Theatre Controls, Inc.) Field-Programmable Gate Arrays PDF资料下载

参数资料

| 型号: | OR2T26A-6S352I |

| 厂商: | Electronic Theatre Controls, Inc. |

| 元件分类: | FPGA |

| 英文描述: | Field-Programmable Gate Arrays |

| 中文描述: | 现场可编程门阵列 |

| 文件页数: | 72/192页 |

| 文件大小: | 3148K |

| 代理商: | OR2T26A-6S352I |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页当前第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页

Data Sheet

June 1999

ORCA Series 2 FPGAs

Lucent Technologies Inc.

163

Timing Characteristics (continued)

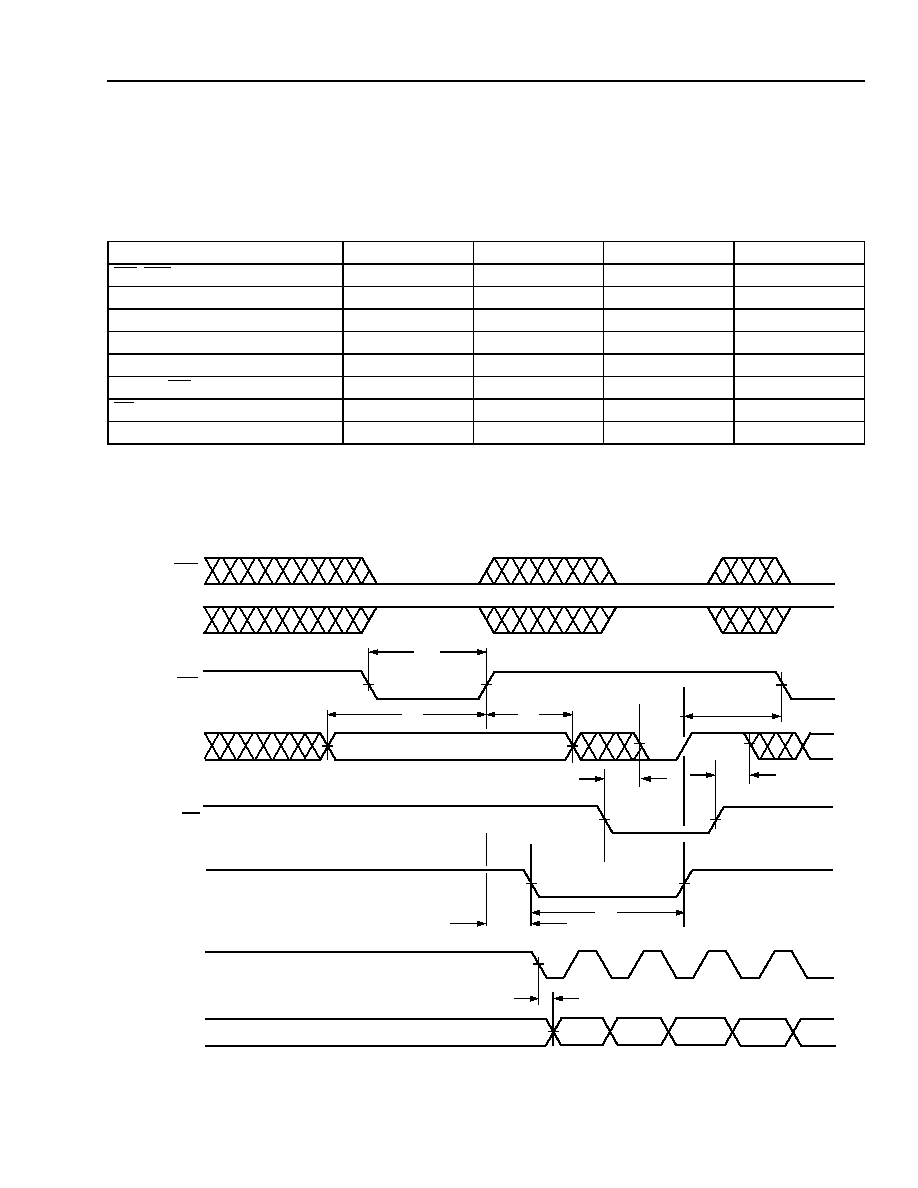

* This parameter is valid whether the end of not RDY is determined from the RDY/RCLK pin or from the D7 pin.

Notes:

Serial data is transmitted out on DOUT on the falling edge of CCLK after the byte is input D[7:0].

D[6:0] timing is the same as the write data port of the D7 waveform because D[6:0] are not enabled.

Figure 68. Asynchronous Peripheral Configuration Mode Timing Diagram

Table 50. Series 2 Asynchronous Peripheral Configuration Mode Timing Characteristics

OR2CxxA Commercial: VDD = 5.0 V ± 5%, 0 °C

≤ TA ≤ 70 °C; OR2CxxA Industrial: VDD = 5.0 V ± 10%, –40 °C ≤ TA ≤ +85 °C.

OR2TxxA/B Commercial: VDD = 3.0 V to 3.6 V, 0 °C

≤ TA ≤ 70 °C; OR2TxxA/B Industrial: VDD = 3.0 V to 3.6 V,

–40 °C

≤ TA ≤ +85 °C.

Parameter

Symbol

Min

Max

Unit

WR

, CS0, and CS1 Pulse Width

TWR

100

—

ns

D[7:0] Setup Time

TS

20

—

ns

D[7:0] Hold Time

TH

0—

ns

RDY Delay

TRDY

—60

ns

RDY Low

TB

18

CCLK Periods

Earliest WR After RDY Goes High*

TWR2

0—

ns

RD

to D7 Enable/Disable

TDEN

—60

ns

CCLK to DOUT

TD

—30

ns

5-4533.a

CS1

D7

CCLK

DOUT

CS0

RDY

D0

D1

D2

TB

TWR

TS

TH

TRDY

WR

D7

TD

PREVIOUS BYTE

TWR2

WRITE DATA

D3

TDEN

RD

相关PDF资料 |

PDF描述 |

|---|---|

| OR2T26A-6S432 | Field-Programmable Gate Arrays |

| OR2T26A-6S432I | Field-Programmable Gate Arrays |

| OR2T26A-6T208 | Field-Programmable Gate Arrays |

| OR2T26A-6T208I | Field-Programmable Gate Arrays |

| OR2T26A-6T240 | Field-Programmable Gate Arrays |

相关代理商/技术参数 |

参数描述 |

|---|---|

| OR2T26A7BA352-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7BC432-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7PS208-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7PS240-DB | 功能描述:FPGA - 现场可编程门阵列 2304 LUT 326 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

| OR2T26A7S208-DB | 功能描述:FPGA - 现场可编程门阵列 Use LatticeEC RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 栅极数量: 逻辑块数量:943 内嵌式块RAM - EBR:1956 kbit 输入/输出端数量:128 最大工作频率:800 MHz 工作电源电压:1.1 V 最大工作温度:+ 70 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-256 |

发布紧急采购,3分钟左右您将得到回复。