- 您现在的位置:买卖IC网 > PDF目录230162 > P4C1281-45CMB (PYRAMID SEMICONDUCTOR CORP) 64K X 4 STANDARD SRAM, 45 ns, CDIP28 PDF资料下载

参数资料

| 型号: | P4C1281-45CMB |

| 厂商: | PYRAMID SEMICONDUCTOR CORP |

| 元件分类: | SRAM |

| 英文描述: | 64K X 4 STANDARD SRAM, 45 ns, CDIP28 |

| 封装: | 0.300 INCH, CERAMIC, DIP-28 |

| 文件页数: | 1/11页 |

| 文件大小: | 862K |

| 代理商: | P4C1281-45CMB |

Document # SRAM136 REV OR

Revised July 2009

P4C1281/P4C1282

ULTRA HIGH SPEED 64K X 4

cmoS STATIc RAmS

FEATURES

Full CMOS, 6T Cell

High Speed (Equal Access and Cycle Times)

– 12/15/20/25 ns (Commercial)

– 15/20/25/35 ns (Industrial)

– 20/25/35/45 ns (Military)

Low Power Operation

5V ± 10% Power Supply

Separate Inputs and Outputs

– P4C1281 Input Data at Outputs during Write

– P4C1282 Outputs in High Z during Write

Fully TTL Compatible Inputs and Outputs

Standard Pinout (JEDEC Approved)

– 28-Pin 300 mil DIP, SOJ

– 28-Pin 350 x 550 mil LCC

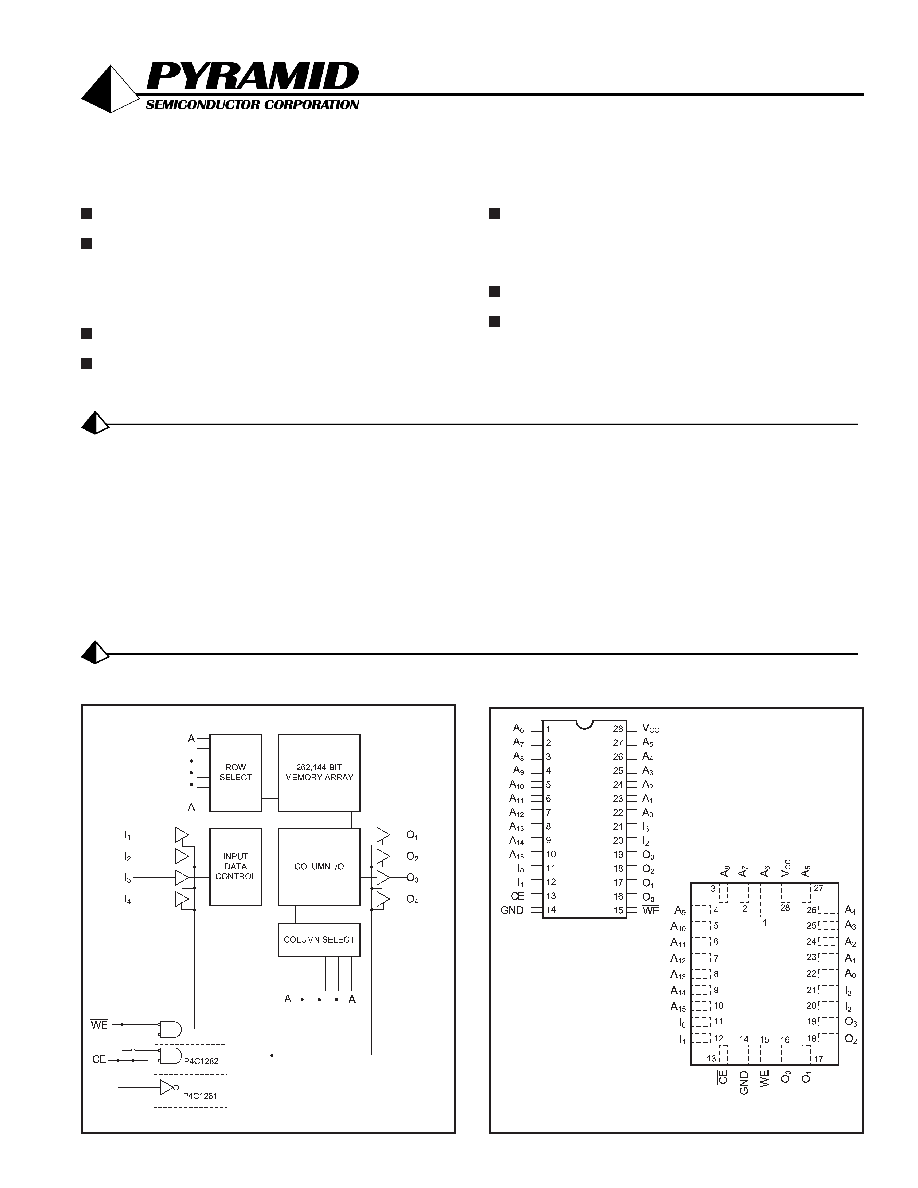

FUnCTIOnAL BLOCk DIAgRAM

PIn COnFIgURATIOnS

DIP (P5, C5, D5-2), SOJ (J5)

DESCRIPTIOn

The P4C1281 and P4C1282 are 262,144-bit (64Kx4) ultra

high-speed static RAMs similar to the P4C1258, but with

separate data I/O pins. The P4C1281 features a transpar-

ent write operation; the outputs of the P4C1282 are in high

impedance during the write cycle. The RAMs operate from

a single 5V ± 10% tolerance power supply.

Access times as fast as 12 nanoseconds are available,

permitting greatly enhanced system operating speeds.

CMOS is used to reduce power consumption.

The P4C1281 and P4C1282 are available in 28-pin 300

mil DIP and SOJ, and a 28-pin 350x550 mil LCC providing

excellent board level densities.

LCC (L5)

相关PDF资料 |

PDF描述 |

|---|---|

| PUMA2E1000MB-15 | 32K X 32 EEPROM 5V MODULE, 150 ns, CPGA66 |

| P4C180-12PC | 4K X 4 CACHE TAG SRAM, 12 ns, PDIP22 |

| PDM41257LA8SO | 256K X 1 STANDARD SRAM, 8 ns, PDSO24 |

| PDM41257SA10SOTR | 256K X 1 STANDARD SRAM, 10 ns, PDSO24 |

| P4C1682-35JC | 4K X 4 STANDARD SRAM, 35 ns, PDSO24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P4C1281-45LM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SRAM |

| P4C1281-45LMB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SRAM |

| P4C1281-55CM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SRAM |

| P4C1281-55CMB | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SRAM |

| P4C1281-55LM | 制造商:未知厂家 制造商全称:未知厂家 功能描述:x4 SRAM |

发布紧急采购,3分钟左右您将得到回复。