- 您现在的位置:买卖IC网 > PDF目录296761 > P89LPC9301FDH (NXP SEMICONDUCTORS) 8-bit microcontroller with accelerated two-clock 80C51 core 4 kB-8 kB 3 V byte-erasable flash PDF资料下载

参数资料

| 型号: | P89LPC9301FDH |

| 厂商: | NXP SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-bit microcontroller with accelerated two-clock 80C51 core 4 kB-8 kB 3 V byte-erasable flash |

| 中文描述: | 8-BIT, FLASH, 18 MHz, MICROCONTROLLER, PDSO28 |

| 封装: | 4.40 MM, PLASTIC, MO-153, SOT-361, TSSOP-28 |

| 文件页数: | 13/66页 |

| 文件大小: | 1326K |

| 代理商: | P89LPC9301FDH |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页

P89LPC9301_931A1

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2010. All rights reserved.

Product data sheet

Rev. 2 — 29 November 2010

20 of 66

NXP Semiconductors

P89LPC9301/931A1

8-bit microcontroller with accelerated two-clock 80C51 core

7.10 CCLK wake-up delay

The P89LPC9301/931A1 has an internal wake-up timer that delays the clock until it

stabilizes depending on the clock source used. If the clock source is any of the three

crystal selections (low, medium and high frequencies) the delay is 1024 OSCCLK cycles

plus 60

sto100 s. If the clock source is the internal RC oscillator, the delay is 200 s to

300

s. If the clock source is watchdog oscillator or external clock, the delay is

32 OSCCLK cycles.

7.11 CCLK modification: DIVM register

The OSCCLK frequency can be divided down up to 510 times by configuring a dividing

register, DIVM, to generate CCLK. This feature makes it possible to temporarily run the

CPU at a lower rate, reducing power consumption. By dividing the clock, the CPU can

retain the ability to respond to events that would not exit Idle mode by executing its normal

program at a lower rate. This can also allow bypassing the oscillator start-up time in cases

where Power-down mode would otherwise be used. The value of DIVM may be changed

by the program at any time without interrupting code execution.

7.12 Low power select

The P89LPC9301/931A1 is designed to run at 18 MHz (CCLK) maximum. However, if

CCLK is 8 MHz or slower, the CLKLP SFR bit (AUXR1.7) can be set to logic 1 to lower the

power consumption further. On any reset, CLKLP is logic 0 allowing highest performance

access. This bit can then be set in software if CCLK is running at 8 MHz or slower.

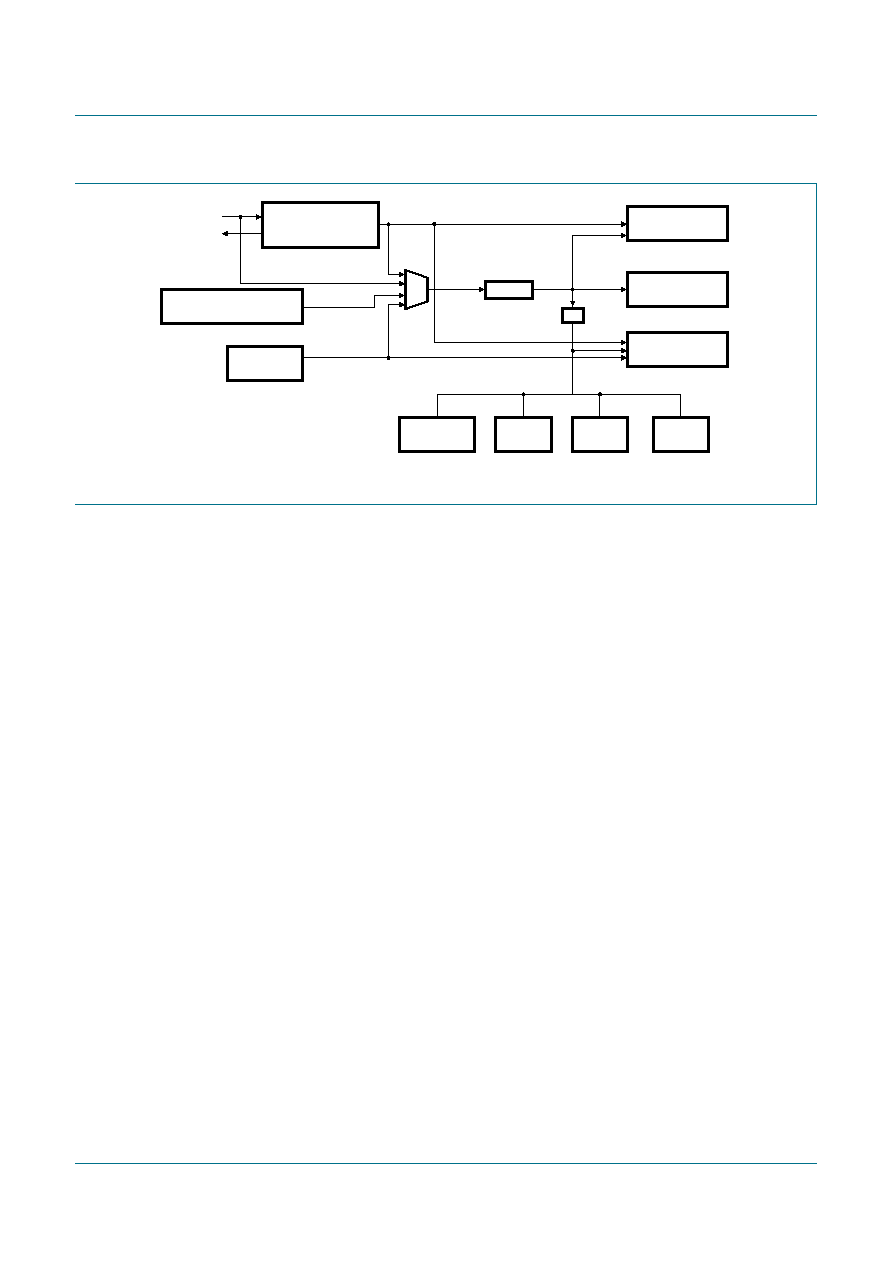

Fig 4.

Block diagram of oscillator control

÷2

002aae452

RTC

CPU

WDT

DIVM

CCLK

UART

OSCCLK

I2C-BUS

PCLK

TIMER 0 AND

TIMER 1

HIGH FREQUENCY

MEDIUM FREQUENCY

LOW FREQUENCY

XTAL1

XTAL2

RC OSCILLATOR

WITH CLOCK DOUBLER

WATCHDOG

OSCILLATOR

(7.3728 MHz/14.7456 MHz

± 1 %)

PCLK

RCCLK

SPI

(400 kHz

± 5 %)

相关PDF资料 |

PDF描述 |

|---|---|

| P89LPC931A1FDH | 8-bit microcontroller with accelerated two-clock 80C51 core 4 kB-8 kB 3 V byte-erasable flash |

| P89LPC930FDH | 8-bit microcontrollers with two-clock 80C51 core 4 kB-8 kB 3 V Flash with 256-byte data RAM |

| P89LPC931FDH | 8-bit microcontrollers with two-clock 80C51 core 4 kB-8 kB 3 V Flash with 256-byte data RAM |

| P89LPC9321FDH | 8-bit microcontroller with accelerated two-clock 80C51 core 8 kB 3 V byte-erasable flash with 512-byte data EEPROM |

| P89LPC932A1FDH | 8-bit microcontroller with accelerated two-clock 80C51 core 8 kB 3 V byte-erasable flash with 512-byte data EEPROM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| P89LPC9301FDH,512 | 功能描述:8位微控制器 -MCU IC 80C51 MCU FLASH 4K RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| P89LPC930FDH | 制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:8-bit microcontrollers with two-clock 80C51 core 4 kB/8 kB 3 V Flash with 256-byte data RAM |

| P89LPC930FDH,129 | 功能描述:8位微控制器 -MCU 80C51 4K FL 256B RAM RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| P89LPC930FDH.129 | 制造商:NXP Semiconductors 功能描述:IC 8BIT MCU 4K FLASH SMD 89LC930 制造商:NXP Semiconductors 功能描述:IC, 8BIT MCU 4K FLASH, SMD, 89LC930 制造商:NXP Semiconductors 功能描述:IC, 8BIT MCU 4K FLASH, SMD, 89LC930; Controller Family/Series:(8051) 8052; Core Size:8bit; No. of I/O's:26; Supply Voltage Min:2.4V; Supply Voltage Max:3.6V; Digital IC Case Style:TSSOP; No. of Pins:28; Program Memory Size:4KB; RAM ;RoHS Compliant: No |

| P89LPC930FDH129 | 制造商:NXP Semiconductors 功能描述:IC 8BIT MCU 80C51 18MHZ TSSOP-28 |

发布紧急采购,3分钟左右您将得到回复。