- 您现在的位置:买卖IC网 > PDF目录69043 > PE3336-21 (PEREGRINE SEMICONDUCTOR CORP) PHASE LOCKED LOOP, 3000 MHz, PQCC44 PDF资料下载

参数资料

| 型号: | PE3336-21 |

| 厂商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 10/16页 |

| 文件大小: | 359K |

| 代理商: | PE3336-21 |

Product Specification

PE3336

Document No. 70-0033-04

│ www.psemi.com

Page 3 of 16

2005-2010 Peregrine Semiconductor Corp. All rights reserved.

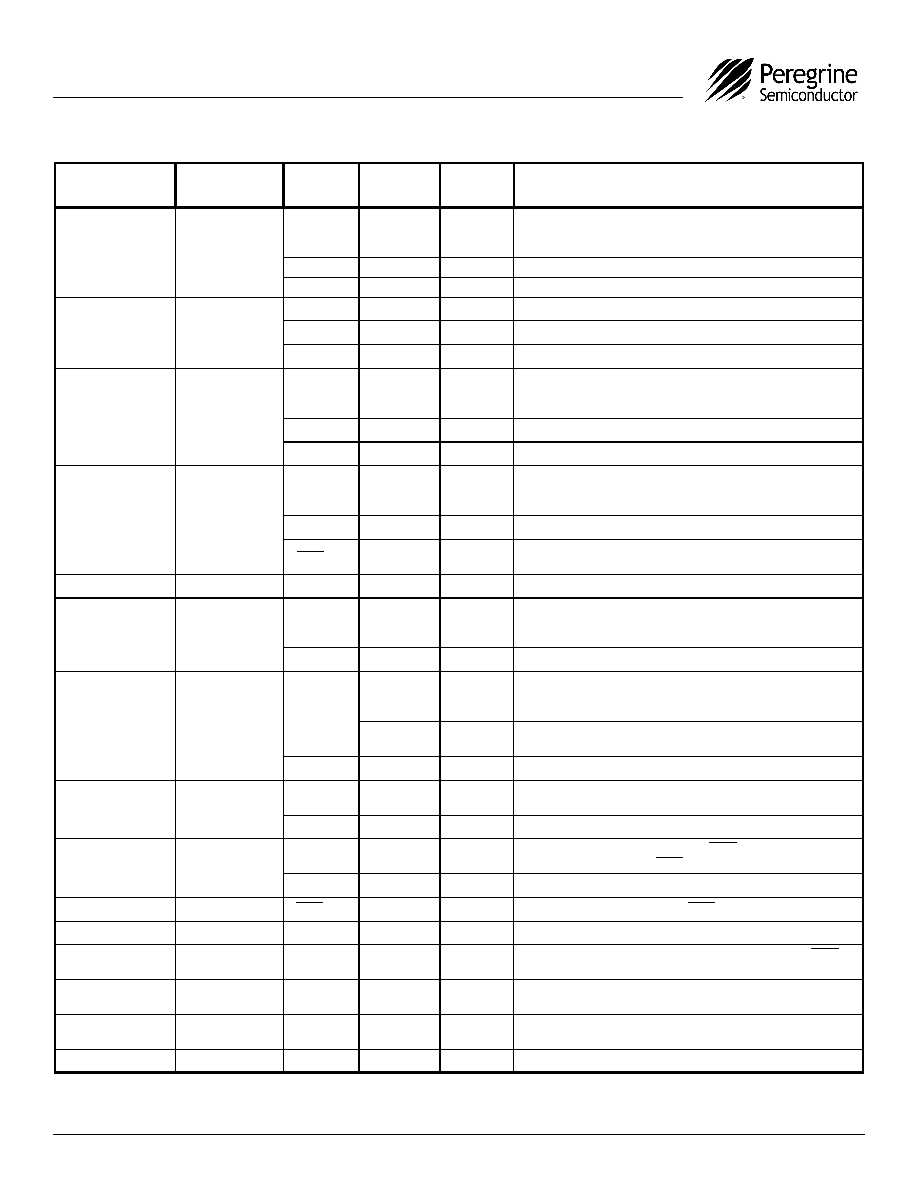

13

7

S_WR

Serial

Input

Serial load enable input. While S_WR is “low”, Sdata can be

serially clocked. Primary register data are transferred to the

secondary register on S_WR or Hop_WR rising edge.

D4

Parallel

Input

Parallel data bus bit4

M4

Direct

Input

M Counter bit4

14

8

Sdata

Serial

Input

Binary serial data input. Input data entered MSB first.

D5

Parallel

Input

Parallel data bus bit5.

M5

Direct

Input

M Counter bit5.

15

9

Sclk

Serial

Input

Serial clock input. Sdata is clocked serially into the 20-bit

primary register (E_WR “low”) or the 8-bit enhancement

register (E_WR “high”) on the rising edge of Sclk.

D6

Parallel

Input

Parallel data bus bit6.

M6

Direct

Input

M Counter bit6.

16

10

FSELS

Serial

Input

Selects contents of primary register (FSELS=1) or secondary

register (FSELS=0) for programming of internal counters while

in Serial Interface Mode.

D7

Parallel

Input

Parallel data bus bit7 (MSB).

Pre_en

Direct

Input

Prescaler enable, active “low”. When “high”, Fin bypasses the

prescaler.

17

11

GND

ALL

Ground.

18

12

FSELP

Parallel

Input

Selects contents of primary register (FSELP=1) or secondary

register (FSELP=0) for programming of internal counters while

in Parallel Interface Mode.

A0

Direct

Input

A Counter bit0 (LSB).

19

13

E_WR

Serial

Input

Enhancement register write enable. While E_WR is “high”,

Sdata can be serially clocked into the enhancement register

on the rising edge of Sclk.

Parallel

Input

Enhancement register write. D[7:0] are latched into the

enhancement register on the rising edge of E_WR.

A1

Direct

Input

A Counter bit1.

20

14

M2_WR

Parallel

Input

M2 write. D[3:0] are latched into the primary register (R[5:4], M

[8:7]) on the rising edge of M2_WR.

A2

Direct

Input

A Counter bit2.

21

15

Smode

Serial,

Parallel

Input

Selects serial bus interface mode (Bmode=0, Smode=1) or

Parallel Interface Mode (Bmode=0, Smode=0).

A3

Direct

Input

A Counter bit3 (MSB).

22

16

Bmode

ALL

Input

Selects direct interface mode (Bmode=1).

23

17,18

VDD

ALL

(Note 1)

Same as pin 1.

24

19

M1_WR

Parallel

Input

M1 write. D[7:0] are latched into the primary register (Pre_en,

M[6:0]) on the rising edge of M1_WR.

25

20

A_WR

Parallel

Input

A write. D[7:0] are latched into the primary register (R[3:0], A

[3:0]) on the rising edge of A_WR.

26

21

Hop_WR

Serial,

Parallel

Input

Hop write. The contents of the primary register are latched

into the secondary register on the rising edge of Hop_WR.

27

22

Fin

ALL

Input

Prescaler input from the VCO. 3.0 GHz max frequency.

Pin No.

(44-lead PLCC)

Pin No.

(48-lead QFN)

Pin

Name

Interface

Mode

Type

Description

Table 1. Pin Descriptions (continued)

相关PDF资料 |

PDF描述 |

|---|---|

| PE3336-00 | PHASE LOCKED LOOP, 3000 MHz, QCC44 |

| PE3336-22 | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| PE3339-12 | PHASE LOCKED LOOP, PDSO20 |

| PE3339-11 | PHASE LOCKED LOOP, PDSO20 |

| PFS726EG | POWER FACTOR CONTROLLER, 95 kHz SWITCHING FREQ-MAX, PZIP6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PE33363LF | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U SMC PLUG RIGHT ANGLE(LEAD FREE) |

| PE3336EK | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3000 MHz UltraCMOS⑩ Integer-N PLL for Low Phase Noise Applications |

| PE33370LF | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG217/U HN MALE TO HN MALE(LEAD FREE) |

| PE33383 | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U BNC MALE TO TNC MALE |

| PE3339 | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3.0 GHz Integer-N PLL for Low Phase Noise Applications |

发布紧急采购,3分钟左右您将得到回复。