- 您现在的位置:买卖IC网 > PDF目录69043 > PE3336-21 (PEREGRINE SEMICONDUCTOR CORP) PHASE LOCKED LOOP, 3000 MHz, PQCC44 PDF资料下载

参数资料

| 型号: | PE3336-21 |

| 厂商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| 封装: | PLASTIC, LCC-44 |

| 文件页数: | 3/16页 |

| 文件大小: | 359K |

| 代理商: | PE3336-21 |

Product Specification

PE3336

Document No. 70-0033-04

│ www.psemi.com

Page 11 of 16

2005-2010 Peregrine Semiconductor Corp. All rights reserved.

PD_U and PD_D drive an active loop filter which

controls the VCO tune voltage. PD_U pulses

result in an increase in VCO frequency; PD_D

pulses result in a decrease in VCO frequency (for

a positive Kv VCO).

A lock detect output, LD is also provided, via the

pin Cext. Cext is the logical “NAND” of PD_U and

PD_D waveforms, which is driven through a series

2 kohm resistor. Connecting Cext to an external

shunt capacitor provides low pass filtering of this

signal. Cext also drives the input of an internal

inverting comparator with an open drain output.

Thus LD is an “AND” function of PD_U and PD_D.

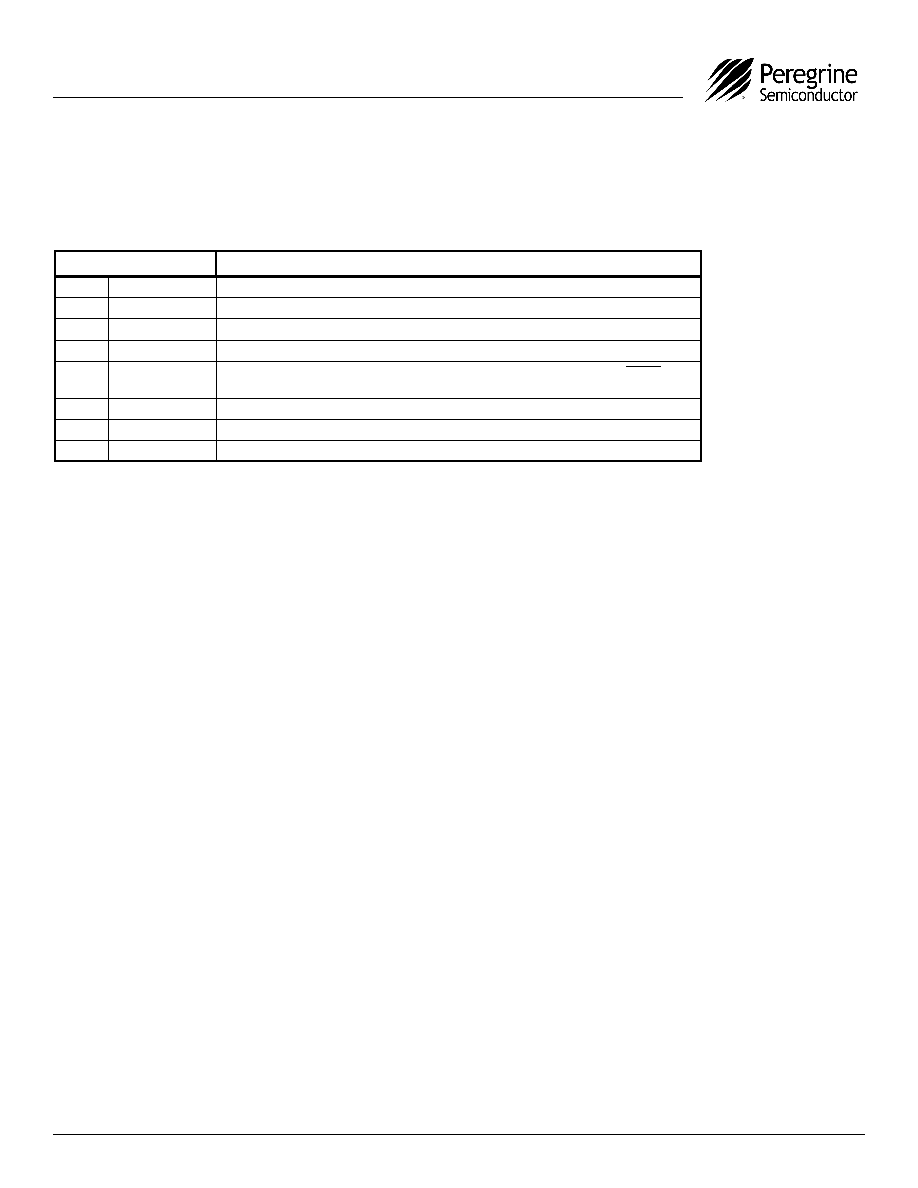

Enhancement Register

The functions of the enhancement register bits are shown below with all bits active “high”.

Table 9. Enhancement Register Bit Functionality

Bit Function

Description

Bit 0

Reserved**

Bit 1

Reserved**

Bit 2

Reserved**

Bit 3

Power down

Power down of all functions except programming interface.

Bit 4

Counter load

Immediate and continuous load of counter programming as directed by the Bmode and

Smode inputs.

Bit 5

MSEL output

Drives the internal dual modulus prescaler modulus select (MSEL) onto the Dout output.

Bit 6

Prescaler output

Drives the raw internal prescaler output onto the Dout output.

Bit 7

fp, fc OE

fp, fc outputs disabled.

** Program to 0

Phase Detector

The phase detector is triggered by rising edges

from the main Counter (fp) and the reference

counter (fc). It has two outputs, PD_U, and PD_D.

If the divided VCO leads the divided reference in

phase or frequency (fp leads fc), PD_D pulses

“low”. If the divided reference leads the divided

VCO in phase or frequency (fc leads fp), PD_U

pulses “low”. The width of either pulse is directly

proportional to phase offset between the two input

signals, fp and fc.

The phase detector gain is equal to 2.7 V / 2

π,

which numerically yields 0.43 V / radian.

相关PDF资料 |

PDF描述 |

|---|---|

| PE3336-00 | PHASE LOCKED LOOP, 3000 MHz, QCC44 |

| PE3336-22 | PHASE LOCKED LOOP, 3000 MHz, PQCC44 |

| PE3339-12 | PHASE LOCKED LOOP, PDSO20 |

| PE3339-11 | PHASE LOCKED LOOP, PDSO20 |

| PFS726EG | POWER FACTOR CONTROLLER, 95 kHz SWITCHING FREQ-MAX, PZIP6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PE33363LF | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U SMC PLUG RIGHT ANGLE(LEAD FREE) |

| PE3336EK | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3000 MHz UltraCMOS⑩ Integer-N PLL for Low Phase Noise Applications |

| PE33370LF | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG217/U HN MALE TO HN MALE(LEAD FREE) |

| PE33383 | 制造商:PASTERNACK 制造商全称:Pasternack Enterprises, Inc. 功能描述:CABLE ASSEMBLY RG316/U BNC MALE TO TNC MALE |

| PE3339 | 制造商:PEREGRINE 制造商全称:PEREGRINE 功能描述:3.0 GHz Integer-N PLL for Low Phase Noise Applications |

发布紧急采购,3分钟左右您将得到回复。