参数资料

| 型号: | PI74SSTVF16859AE |

| 厂商: | Pericom |

| 文件页数: | 1/8页 |

| 文件大小: | 0K |

| 描述: | IC REG BUFFER 13-26BIT 64-TSSOP |

| 标准包装: | 28 |

| 系列: | 74SSTVF |

| 逻辑类型: | 13 位至 26 位寄存缓冲器,DDR |

| 电源电压: | 2.3 V ~ 2.7 V |

| 位数: | 13,26 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-TFSOP (0.240",6.10mm 宽) |

| 供应商设备封装: | 64-TSSOP |

| 包装: | 管件 |

1

PS8657C

10/07/08

ProductDescription

PericomSemiconductor’sPI74SSTVF16859logiccircuitisproduced

using the Company’s advanced sub-micron CMOS technology,

achieving industry leading speed.

All inputs are compatible with the JEDEC standard for SSTL_2,

except the LVCMOS reset (RESET) input. All outputs are SSTL_2,

Class II compatible.

The device operates from a differential clock (CLK and CLK). Data

registeredatthecrossingofCLKgoingHIGH,andCLKgoingLOW.

ThePI74SSTVF16859supportslow-powerstandbyoperation.When

RESET is LOW, the differential input receivers are disabled, and

undriven (floating) data, clock and reference voltage (VREF) inputs

are allowed. In addition, when RESET is LOW, all registers are reset,

and all outputs are forced LOW. The LVCMOS RESET input must

always be held at a valid logic HIGH or LOW level.

To ensure defined outputs from the register before a stable clock

has been supplied, RESET must be held in the LOW state during

power up.

In the DDR DIMM application, RESET is specified to be completely

asynchronous with respect to CLK and CLK. Therefore, no timing

relationship can be guaranteed between the two. When entering

RESET, the register will be cleared and the outputs will be driven

LOW quickly, relative to the time to disable the differential input

receivers, thus ensuring no glitches on the output. However, when

comingoutof RESET,theregisterwillbecomeactivequickly,relative

to the time to enable the differential input receivers. When the data

inputs are LOW, and the clock is stable, during the time from the

LOW-to-HIGH transition of RESET until the input receivers

are fully enabled, the design must ensure that the outputs will

remainLOW.

Pericom’s PI74SSTVF16859 is characterized for operation from

0°Cto70°C.

ProductFeatures

PI74 SSTVF16859 is designed for low-voltage operation,

2.5VforPC1600~PC2700;2.6VforPC3200

Supports SSTL_2 Class I specifications on outputs

All Inputs are SSTL_2 Compatible, except RESET

whichisLVCMOS.

Designed for DDR Memory

Flow-Through Architecture

Packages:

56-pin, Plastic Very Thin Fine Pitch Quad Flat

No Lead QFN (ZB)

(Lead-free packages are available)

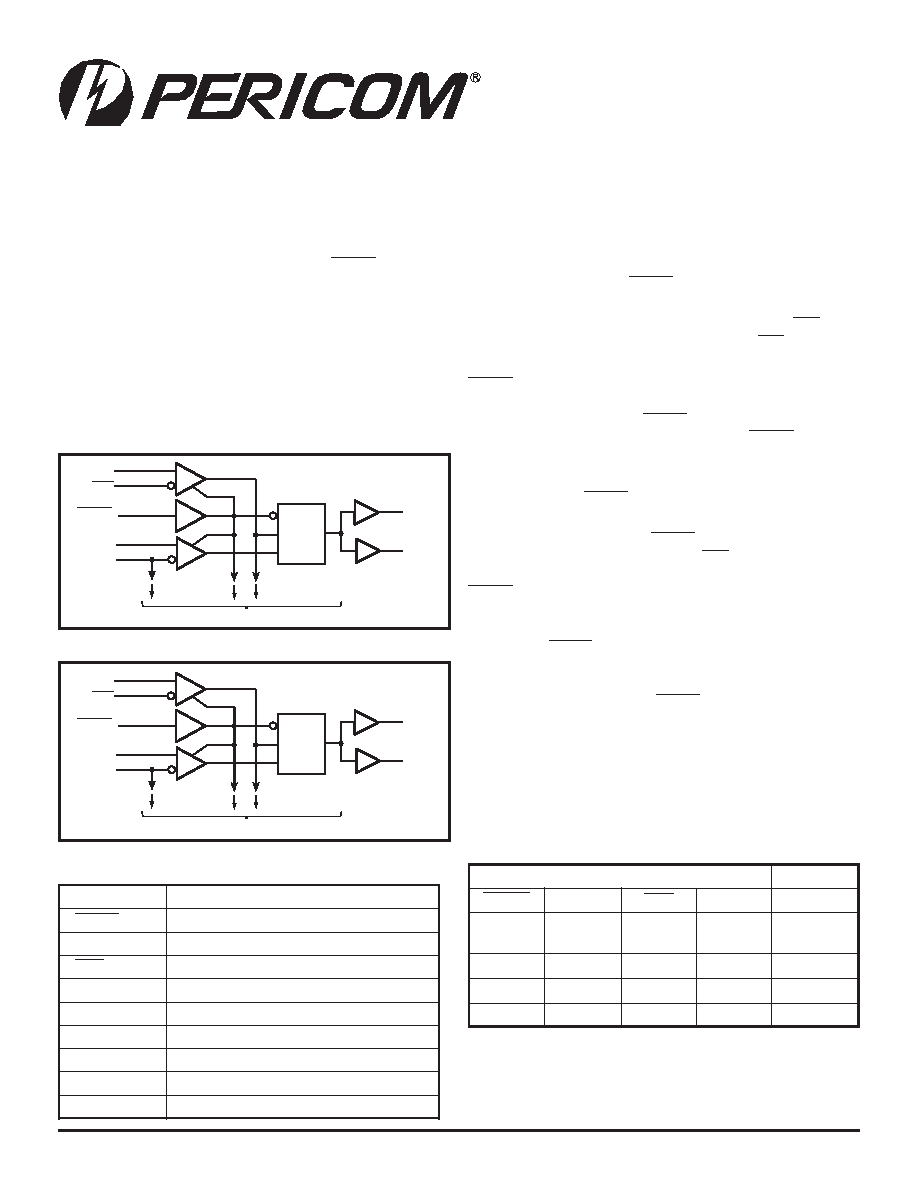

Logic Block Diagram - TSSOP

ProductPinDescription

12345678901234567890123456789012123456789012345678901234567890121234567890123456789012345678901212345678901234567890123456789012123456789012

PI74SSTVF16859

13-Bit to 26-Bit Registered Buffer

TO 12 OTHER CHANNELS

RESET

CLK

48

49

VREF

D1

35

45

D

R

CLK

Q1A

16

Q1B

32

CLK

V

51

Logic Block Diagram - QFN

TO 12 OTHER CHANNELS

RESET

CLK

35

36

VREF

D1

24

32

D

R

CLK

Q1A

7

Q1B

22

CLK

V

38

s

t

u

p

n

Is

t

u

p

t

u

O

T

E

S

E

RK

L

CK

L

CD

Q

L

r

o

X

g

n

it

a

o

l

F

r

o

X

g

n

it

a

o

l

F

r

o

X

g

n

it

a

o

l

F

L

H

↑↓

HH

Η↑

↓

LL

HH

r

o

LH

r

o

LX

o

Q

)

2

(

Truth

Table(1)

Notes:

1. H = High Signal Level

L = Low Signal Level

↑ = Transition LOW-to-HIGH

↓ = Transition HIGH-to-LOW

X = Irrelevant or floating

2. Output level before the

indicated steady state

input conditions were

established.

e

m

a

N

n

i

Pn

o

i

t

p

i

r

c

s

e

D

T

E

S

E

RS

O

M

C

V

L

)

w

o

L

e

v

it

c

A

(

t

e

s

e

R

K

L

Ct

u

p

n

I

l

a

it

n

e

r

e

f

fi

D

e

v

it

i

s

o

P

,t

u

p

n

I

k

c

o

l

C

K

L

Ct

u

p

n

I

l

a

it

n

e

r

e

f

fi

D

e

v

it

a

g

e

N

,t

u

p

n

I

k

c

o

l

C

D3

1

D

-

1

D

,t

u

p

n

I

a

t

a

D

Q3

1

Q

-

1

Q

,t

u

p

t

u

O

a

t

a

D

N

Gd

n

u

o

r

G

V D

D

e

g

a

tl

o

V

y

l

p

u

S

e

r

o

C

V Q

D

e

g

a

tl

o

V

y

l

p

u

S

t

u

p

t

u

O

V F

E

R

e

g

a

tl

o

V

e

c

n

e

r

e

f

e

R

t

u

p

n

I

08-0291

相关PDF资料 |

PDF描述 |

|---|---|

| PI74SSTVF16859AZBE | IC REG BUFFER 13-26BIT 56-QFN |

| PI74STX1G02CX | IC SINGLE 2-IN NOR GATE SC70-5 |

| PI74STX1GU04CEX | IC UNBUFFERED INVERTER SC70-5 |

| PI74STX4G4245ZJEX | IC 2BIT LVL SHFT BUF/TXRX 16TDFN |

| PI90LVB16L | IC CLOCK BUFFER MUX 1:6 24-TSSOP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PI74SSTVF16859AEX | 功能描述:寄存器 13/26B Registered Buffer RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| PI74SSTVF16859AX | 制造商:Pericom Semiconductor Corporation 功能描述:Registered Buffer Single 13-CH CMOS 64-Pin TSSOP T/R |

| PI74SSTVF16859AZBE | 功能描述:IC REG BUFFER 13-26BIT 56-QFN RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:74SSTVF 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| PI74SSTVF16859AZBEX | 制造商:Pericom Semiconductor Corporation 功能描述:Registered Buffer Single 13-CH CMOS 56-Pin TQFN EP T/R |

| PI74SSTVF32852ANBE | 功能描述:寄存器 24B to 48B Registered RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。