- 您现在的位置:买卖IC网 > PDF目录378053 > PM5307 (PMC-Sierra, Inc.) 9.953 Gbit/s Telecom Bus Serializer PDF资料下载

参数资料

| 型号: | PM5307 |

| 厂商: | PMC-Sierra, Inc. |

| 英文描述: | 9.953 Gbit/s Telecom Bus Serializer |

| 中文描述: | 9.953 Gbit / s的串行总线通信 |

| 文件页数: | 1/2页 |

| 文件大小: | 312K |

| 代理商: | PM5307 |

PM5307

TBS-9953

Advance

9.953 Gbit/s Telecom Bus Serializer

PMC-2001266 (A2)

PROPRIETARY AND CONFIDENTIAL TO PMC

-

SIERRA, INC., AND FOR ITS CUSTOMERS

’

INTERNAL USE

Copyright PMC

-

Sierra, Inc. 2001.

FEATURES

The PM5307 TBS-9953 switches

timeslots (down to an STS-1 granularity)

from/to the line side interface to/from a

system side working (W), protection (P),

and optionally an auxiliary (A) interface.

4 sets of 16 port serial links:

2 sets of 16 x 777.6 Mbit/s links

(8B/10B encoded Serial

TelecomBus).

2 set of configurable 16 x 777.6

Mbit/s or 16 x 2.488 Gbit/s

(SONET/SDH scrambled).

Typical applications (line to system

interfaces):

16 x 777.6 Mbit/s to 3 x 16 x 777.6

Mbit/s (W,P,A)

16 x 777.6 Mbit/s to 4x4x2.488

Gbit/s (W,P,A1,A2)

2 x (16 x 777.6) Mbit/s to

2 x (2 x 4 x 2.488) Gbit/s (W, P) -

Dual TBS

4 x 2.488 Gbit/s to 3 x 4 x 2.488

Gbit/s (W,P,A)

Supports redundant working/protection

time-space-time switch fabrics,

including the PM5372 TSE and

PM5374 TSE-160 devices.

Supports STS-192c/STM-64c, STS-

48c/STM-16c, STS-12c/STM-4c, and

STS-3c/STM-1c traffic on the interface.

Supports through-traffic, drop-traffic

and protection switching in UPSR,

2-fiber BLSR and 4-fiber BLSR

applications.

Provides per link concatenated

SONET PRBS generation/ monitoring

for outgoing/ incoming LVDS data link

for off-line link verification. 777.6 Mbit/s

links can carry an STS-12c PRBS

stream. 2.488 Gbit/s links can carry an

STS-48c PRBS stream.

Option to perform in-service link

verification by checking and/or

overwriting the Z2 byte of each

constituent STS-1/STM-0 frame with a

unique software programmable byte

and its complement.

Provides pins to coordinate updating of

the connection map of the time-slot

interchange blocks in the local device,

peer PM5307 TBS-9953 devices, and

companion PM5374 TSE-160 or

PM5372 TSE devices.

Provides two independent time

domains for frame alignment

purposes. The time domains for each

link interface are selectable through

the software interface.

Driven by a 155.52 MHz reference

clock.

Implemented in 1.8 V core and 3.3 V

I/O, 0.18 μm CMOS and packaged in a

1152 ball FCBGA.

Provides a standard IEEE 1149.1

JTAG port.

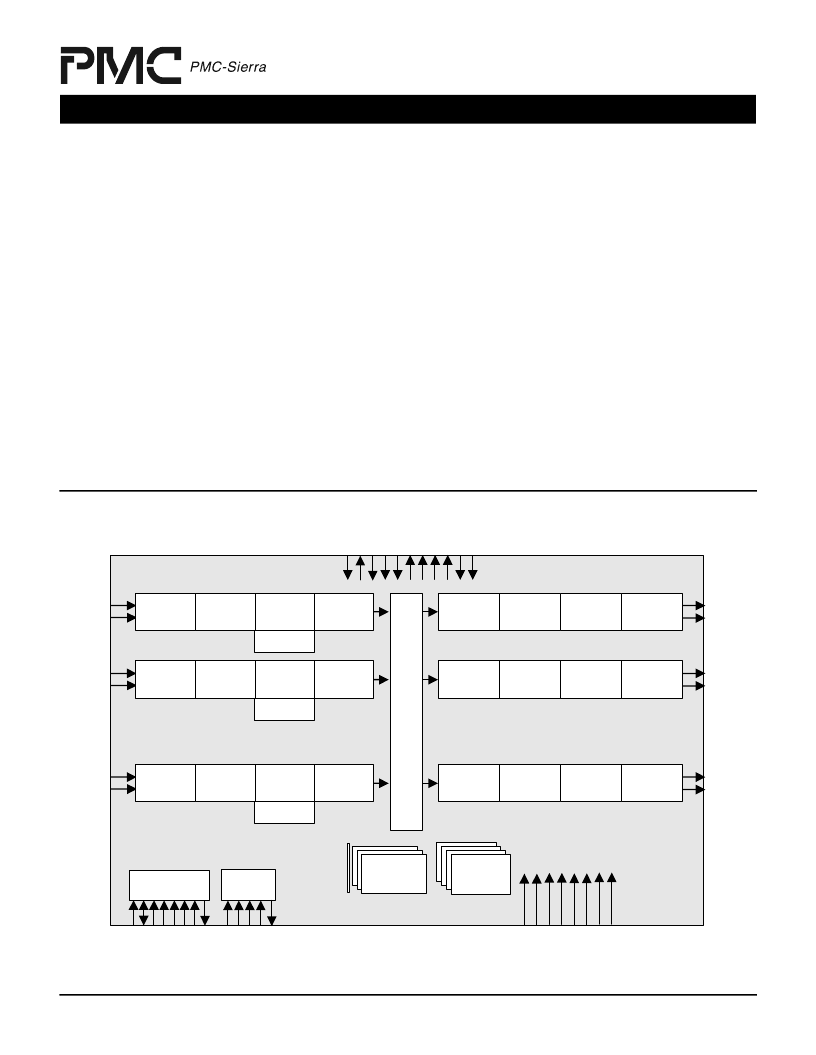

Clock

Synthesis

Unit Interface

(CSUI)

D

I

A

R

A

C

W

R

Microprocessor

Interface

JTAG

T

T

T

T

T

Cross-

Bar

Space

Switch

Element

(SSWE)

Clock

SSyClock

USynthesis

Unit (CSU)

RP[1]

RN[1]

Transmit LVDS

(TXLV) #1

Serializer

(PISO) #1

Tx Data

Scrambler/

Encoder (TSEC)

#1

Tx Time Slot

Interchange

(TTSI) #1

Rx Time Slot

Interchange

(RTSI) #1

Rx SONET

Data Framer

(RSEF) #1

Data Recovery

Unit (DRU) #1

Receive LVDS

(RXLV) #1

TP[1]

TN[1]

RP[2]

RN[2]

Transmit LVDS

(TXLV) #2

Serializer

(PISO) #2

Tx Data

Scrambler/

Encoder (TSEC)

#2

Tx Time Slot

Interchange

(TTSI) #2

Rx Time Slot

Interchange

(RTSI) #2

Rx SONET

Data Framer

(RSEF) #2

Data Recovery

Unit (DRU) #2

Receive LVDS

(RXLV) #2

TP[2]

TN[2]

RP[65]

RN[65]

Transmit LVDS

(TXLV) #65

Serializer

(PISO) #65

Tx Data

Scrambler/

Encoder (TSEC)

#65

Tx Time Slot

Interchange

(TTSI) #65

Rx Time Slot

Interchange

(RTSI) #65

Rx SONET

Data Framer

(RSEF) #65

Data Recovery

Unit (DRU) #65

Receive LVDS

(RXLV) #65

TP[65]

TN[65]

R

C

S

O

C

R

R

T

T

T

T

R

R

R

R

PRBS Monitor

(PIPM) #65

PRBS Monitor

(PIPM) #2

PRBS Monitor

(PIPM) #1

R

R

R

R

BLOCK DIAGRAM

相关PDF资料 |

PDF描述 |

|---|---|

| PM5309 | Multi-rate Telecom Backplane SERDES for 2.5 Gbit/s Interconnect |

| PM5310 | CONNECTOR |

| PM5312 | SONET/SDH Transport Overhead Terminating Transceiver |

| PM5313 | SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S |

| PM5313-BI | SONET/SDH PAYLOAD EXTRACTOR/ALIGNER FOR 622 MBIT/S |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PM5309 | 制造商:PMC 制造商全称:PMC 功能描述:Multi-rate Telecom Backplane SERDES for 2.5 Gbit/s Interconnect |

| PM531 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Analog IC |

| PM5310 | 制造商:PMC 制造商全称:PMC 功能描述:TelecomBus Serializer for 2.5 Gbit/s Interconnect |

| PM5310BI | 制造商:PMC-Sierra 功能描述: |

发布紧急采购,3分钟左右您将得到回复。