- 您现在的位置:买卖IC网 > PDF目录368231 > PSD603E1 Field Programmable Microcontroller Peripherals with Embedded Micro--Cell(可编程逻辑,4K位SRAM,26个可编程I/O,通用PLD有63个输入) PDF资料下载

参数资料

| 型号: | PSD603E1 |

| 英文描述: | Field Programmable Microcontroller Peripherals with Embedded Micro--Cell(可编程逻辑,4K位SRAM,26个可编程I/O,通用PLD有63个输入) |

| 中文描述: | 现场可编程微控制器外围设备和嵌入式微-细胞(可编程逻辑,4K的位的SRAM,26我个可编程输入/输出,通用PLD的有63个输入) |

| 文件页数: | 9/84页 |

| 文件大小: | 426K |

| 代理商: | PSD603E1 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

PSD6XX Family

11-9

PSD6XX devices consist of several major functional blocks. Figure 2 shows the

architecture of the PSD6XX device family. The functions of each block are described briefly

in the following sections. Many of the blocks perform multiple functions, and are user

configurable.

PLDs

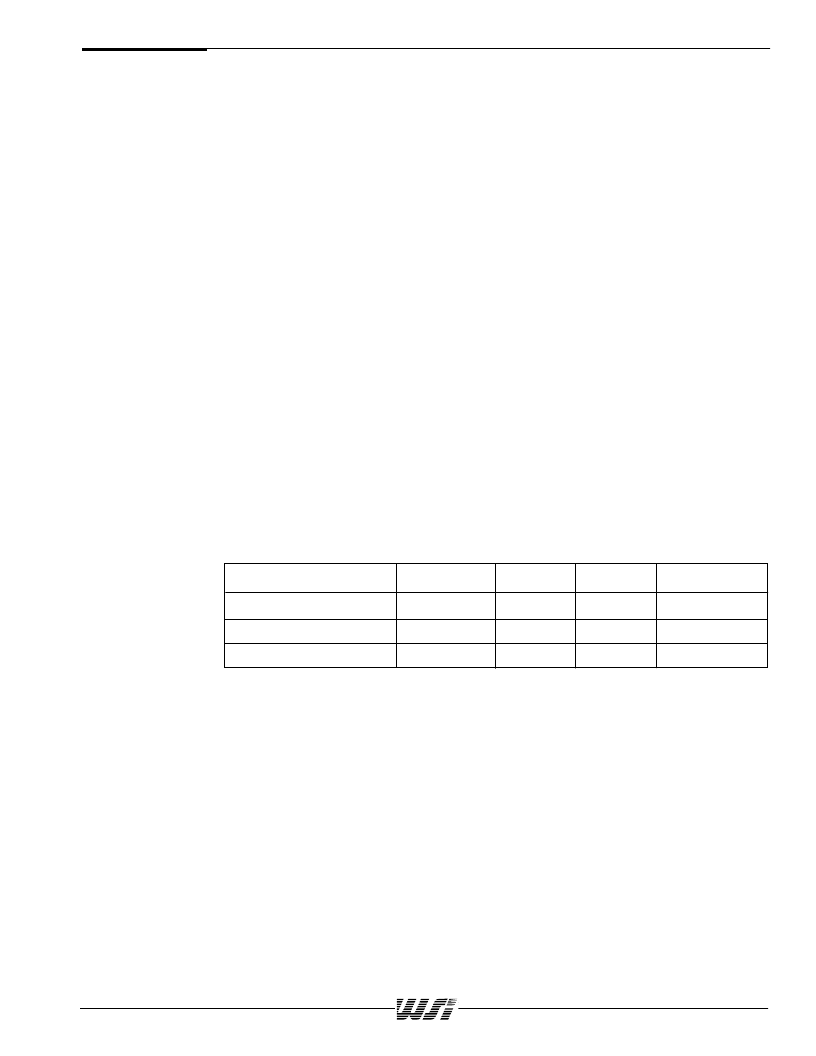

The device contains three PLD blocks each optimized for a different function as shown in

Table 5. The functional partitioning of the PLDs reduces power consumption, optimizes

cost/performance and ease of design entry.

The Decode PLD (DPLD) is used to decode and generate chip selects for the PSD6XXE1

internal memory, registers and peripheral mode. The External Chip Select PLD (ECSPLD)

is optimized to generate chip selects for devices external to the PSD6XXE1. The General

Purpose PLD (GPLD) can implement user defined logic functions. The DPLD and ECSPLD

have combinatorial outputs while the GPLD has 12 Output Micro

Cells. The PSD6XXE1

also has 23 Input Micro

Cells that can be configured as inputs to the PLD. The PLDs

receive their inputs from the PLD Input bus and are differentiated by their output

destinations, number of product terms, and Micro

Cells.

I/O Ports

The PSD6XXE1 has 26 I/O pins divided among four ports. Each I/O pin can be individually

configured to provide many functions. Ports A, B, C and D can be configured as standard

MCU I/O ports, PLD I/O, or latched address outputs for microcontrollers using multiplexed

address/data busses.

Ports A and B can also be configured as a data port for microcontrollers with a

non-multiplexed bus. In these modes, Port A is connected to D0–7 and Port B to D8–15.

PSD6XXE1

Architectural

Overview

Name

Abbreviation

Inputs

Outputs

Product Terms

Decode PLD

DPLD

63

12

13

External Chip Select PLD

ECSPLD

24

7

7

General PLD

GPLD

63

12

109

Table 5.

相关PDF资料 |

PDF描述 |

|---|---|

| PSD612E1 | Field Programmable Microcontroller Peripherals with Embedded Micro--Cell(可编程逻辑,4K位SRAM,26个可编程I/O,通用PLD有63个输入) |

| PSD613E1 | Field Programmable Microcontroller Peripherals with Embedded Micro--Cell(可编程逻辑,4K位SRAM,26个可编程I/O,通用PLD有63个输入) |

| PSD703S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD701S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD702S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD603E1-70L | 制造商:WSI 功能描述: |

| PSD60-A | 制造商:WALL 制造商全称:Wall Industries,Inc. 功能描述:60 Watt Dual Output AC/DC Power Supply |

| PSD60-B | 制造商:WALL 制造商全称:Wall Industries,Inc. 功能描述:60 Watt Dual Output AC/DC Power Supply |

| PSD61 | 制造商:POWERSEM 制造商全称:POWERSEM 功能描述:Three Phase Rectifier Bridges |

| PSD611E1-15J | 制造商:WSI 功能描述: 制造商:WSI 功能描述:32K X 8 OTPROM, 26 I/O, PIA-GENERAL PURPOSE, PQCC52 |

发布紧急采购,3分钟左右您将得到回复。