- 您现在的位置:买卖IC网 > PDF目录368231 > PSD703S5 Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) PDF资料下载

参数资料

| 型号: | PSD703S5 |

| 英文描述: | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| 中文描述: | 现场可编程微控制器外围设备具有监督职能(可编程逻辑,4K的位的SRAM,27余个可编程输入/输出,通用PLD的有66个输入) |

| 文件页数: | 18/104页 |

| 文件大小: | 515K |

| 代理商: | PSD703S5 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

PSD7XX Family

13-18

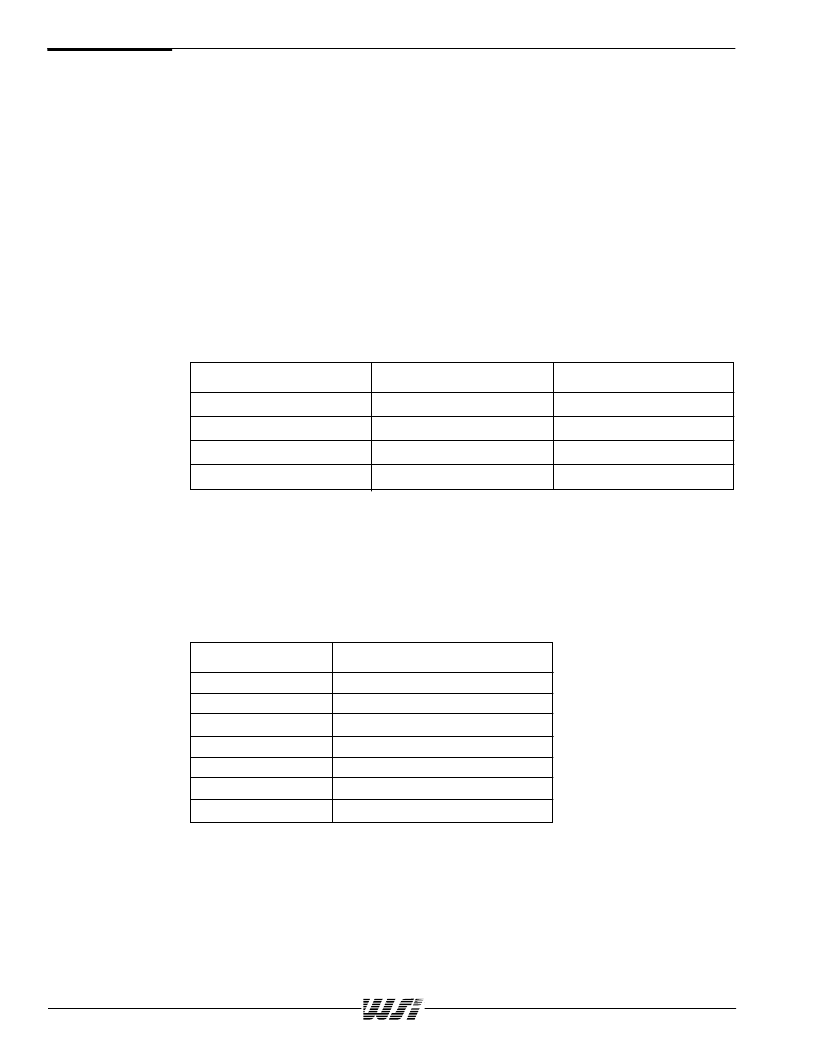

ECSPLD Output

Port A, B, or D Assignments

ECS0

ECS1

ECS2

ECS3

ECS4

ECS5

ECS6

PA0, PB0

PA1, PB1

PA2, PB2

PA3, PB3

PD0*

PD1*

PD2*

Table 10. ECSPLD Output Port Assignments

The seven ECSPLD outputs may be driven off the device through Ports A, B, or D, as

shown in Table 10, via the Micro

Cell Allocator. Port selection is specified in the PSDabel

file or assigned by the PSDcompiler.

PLDs

(cont.)

*

Port D has no output enable (.oe) product terms for ECS4-6 outputs.

External Chip Select PLD

The External Chip Select PLD (ECSPLD) provides the means to select external devices.

The output buffer of the ECSPLD can be configured to operate in high slew rate by writing a

“1” to the corresponding bit in the Drive Register. The slew rate is a measurement of the

rise and fall times of the output. A higher slew rate means a faster output response while a

lower slew rate is a slower response. Refer to Table 26 in the I/O Section for setting up the

Drive Register.

Faster transitions are more likely to cause line reflections and system noise than slower

rates. Adjusting the slew rate allows a trade-off between greater speed and noise

sensitivity. The selection should be based on the performance requirements of the system

and its noise characteristics. Set the corresponding bits in the Drive Register to “0” (for

normal speed) or “1” (for fast drive). The default value is zero.

The ECSPLD has 24 inputs as shown in Table 9. Its outputs are combinatorial, of either

polarity, and have one product term each as shown in Figure 5.

Input Source

Input Name

Number of Bits

MCU Address Bus

A[15:0]*

16

MCU Control Signals

CNTL[2:0]

3

Power Down Signal

PDN**

1

Page Register

PGR[3:0]

4

Table 9. ECSPLD Inputs

*

*

In 80C51XA mode, the address inputs are A[19:4]

**

APD output. When PDN is high, the PSD7XX is in power down mode

相关PDF资料 |

PDF描述 |

|---|---|

| PSD701S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD702S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD711S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD712S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

| PSD713S5 | Field Programmable Microcontroller Peripherals with Supervisory Functions(可编程逻辑,4K位SRAM,27个可编程I/O,通用PLD有66个输入) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD705 | 制造商:PACELEADER 制造商全称:PACELEADER INDUSTRIAL 功能描述:SURFACE MOUNT SCHOTTKY BARRIER DIODES |

| PSD706 | 制造商:PACELEADER 制造商全称:PACELEADER INDUSTRIAL 功能描述:SURFACE MOUNT SCHOTTKY BARRIER DIODES |

| PSD711S5-15L | 制造商:WSI 功能描述: |

| PSD711S5-70L | 制造商:WSI 功能描述: |

| PSD712S5-15L | 制造商:WSI 功能描述: |

发布紧急采购,3分钟左右您将得到回复。