- 您现在的位置:买卖IC网 > PDF目录378075 > PSD813F2V-12J (意法半导体) Flash In-System Programmable ISP Peripherals For 8-bit MCUs PDF资料下载

参数资料

| 型号: | PSD813F2V-12J |

| 厂商: | 意法半导体 |

| 英文描述: | Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| 中文描述: | Flash在系统可编程ISP的外设的8位微控制器 |

| 文件页数: | 22/110页 |

| 文件大小: | 1685K |

| 代理商: | PSD813F2V-12J |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

PSD813F1

22/110

READ

Under typical conditions, the microcontroller may

read the Flash or EEPROM memory using READ

operations just as it would a ROM or RAM device.

Alternately, the microcontroller may use READ op-

erations to obtain status information about a Pro-

gram or Erase operation in progress. Lastly, the

microcontroller may use instructions to read spe-

cial data from these memories. The following sec-

tions describe these READ functions.

Read Memory Contents.

Main Flash is placed in

the READ mode after power-up, chip reset, or a

Reset Flash instruction (see

Table 8., page 20

).

The microcontroller can read the memory contents

of main Flash or EEPROM by using READ opera-

tions any time the READ operation is not part of an

instruction sequence.

Read Main Flash Memory Identifier.

The main

Flash memory identifier is read with an instruction

composed of 4 operations:

3 specific write operations and a READ operation

(see Table

8

). During the READ operation, ad-

dress bits A6, A1, and A0 must be 0,0,1, respec-

tively, and the appropriate sector select signal

(FSi) must be active. The Flash ID is E3h for the

PSD. The MCU can read the ID only when it is ex-

ecuting from the EEPROM.

Read Main Flash Memory Sector Protection

Status.

The main Flash memory sector protection

status is read with an instruction composed of 4

operations: 3 specific WRITE operations and a

READ operation (see

Table 8., page 20

). During

the READ operation, address bits A6, A1, and A0

must be 0,1,0, respectively, while the chip select

FSi designates the Flash sector whose protection

has to be verified. The READ operation will pro-

duce 01h if the Flash sector is protected, or 00h if

the sector is not protected.

The sector protection status for all NVM blocks

(main Flash or EEPROM) can be read by the mi-

crocontroller accessing the Flash Protection and

PSD/EE Protection registers in PSD I/O space.

See

Flash Memory and EEPROM Sector

Protect, page 30

for register definitions.

Reading the OTP Row.

There are 64 bytes of

One-Time-Programmable (OTP) memory that re-

side in EEPROM. These 64 bytes are in addition

to the 32 Kbytes of EEPROM memory. A READ of

the OTP row is done with an instruction composed

of at least 4 operations: 3 specific WRITE opera-

tions and one to 64 READ operations (see

Table

8., page 20

). During the READ operation(s), ad-

dress bit A6 must be zero, while address bits A5-

A0 define the OTP Row byte to be read while any

EEPROM sector select signal (EESi) is active. Af-

ter reading the last byte, an EEPROM Return in-

struction

must

be

executed

8., page 20

).

Reading the Erase/Program Status Bits.

The

PSD provides several status bits to be used by the

microcontroller to confirm the completion of an

erase or programming instruction of Flash memo-

ry. Bits are also available to show the status of

WRITES to EEPROM. These status bits minimize

the time that the microcontroller spends perform-

ing these tasks and are defined in Table

9

. The

status bits can be read as many times as needed.

For Flash memory, the microcontroller can per-

form a READ operation to obtain these status bits

while an Erase or Program instruction is being ex-

ecuted by the embedded algorithm. See the sec-

tion

entitled

PROGRAMMING

MEMORY, page 27

for details.

For EEPROM not in SDP mode, the microcontrol-

ler can perform a READ operation to obtain these

status bits just after a data WRITE operation. The

microcontroller may write one to 64 bytes before

reading the status bits. See the section entitled

Writing to the EEPROM, page 24

for details.

For EEPROM in SDP mode, the microcontroller

will perform a READ operation to obtain these sta-

tus bits while an SDP write instruction is being ex-

ecuted by the embedded algorithm. See section

entitled

EEPROM

Software

(SDP), page 24

for details.

(see

Table

FLASH

Data

Protect

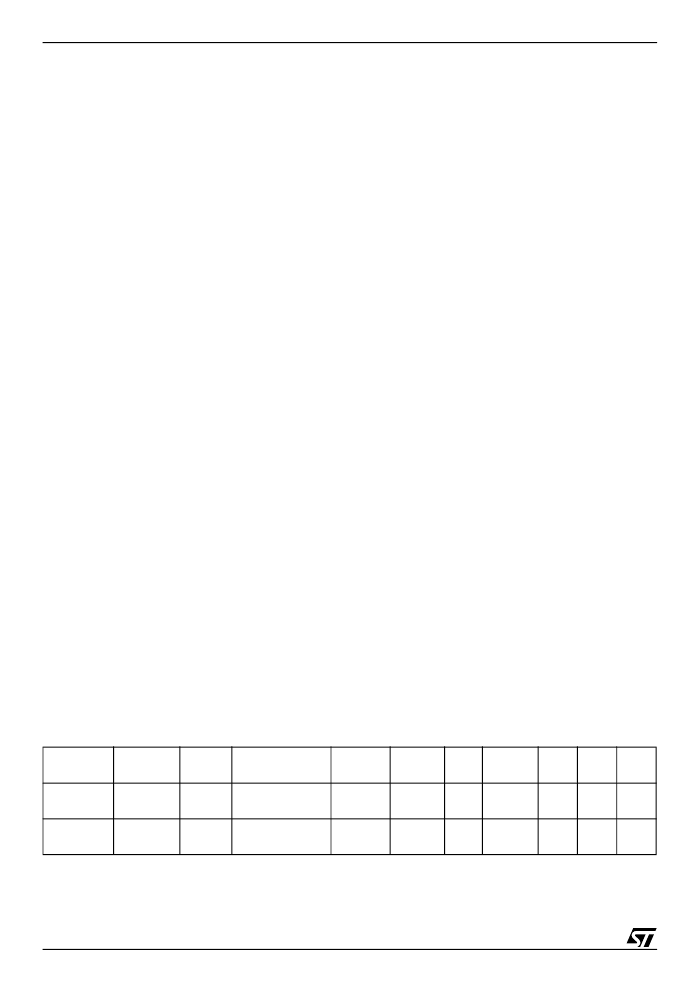

Table 9. Status Bit

Note: 1. X = not guaranteed value, can be read either 1 or 0.

2. DQ7-DQ0 represent the Data Bus Bits, D7-D0.

3. FSi and EESi are active High.

Device

FSi/

CSBOOTi

EESi

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

Flash

V

IH

V

IL

Data Polling

Toggle

Flag

Error

Flag

X

Erase

Timeout

X

X

X

EEPROM

V

IL

V

IH

Data Polling

Toggle

Flag

X

X

X

X

X

X

相关PDF资料 |

PDF描述 |

|---|---|

| PSD813F1A-12J | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD813F1A-12JI | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD813F1A-12JT | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD813F4-12 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

| PSD813F4-15 | Flash In-System Programmable (ISP) Peripherals for 8-bit MCUs, 5V |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PSD813F2V-12J1T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash in-system programmable (ISP) peripherals for 8-bit MCUs, 3.3 V |

| PSD813F2V-12JI | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813F2V-12JIT | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813F2V-12JT | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

| PSD813F2V-12M | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:Flash In-System Programmable ISP Peripherals For 8-bit MCUs |

发布紧急采购,3分钟左右您将得到回复。