- 您现在的位置:买卖IC网 > PDF目录380637 > R1Q3A3609ABG-40R (Renesas Technology Corp.) 36-Mbit QDR™II SRAM 4-word Burst PDF资料下载

参数资料

| 型号: | R1Q3A3609ABG-40R |

| 厂商: | Renesas Technology Corp. |

| 英文描述: | 36-Mbit QDR™II SRAM 4-word Burst |

| 文件页数: | 6/26页 |

| 文件大小: | 407K |

| 代理商: | R1Q3A3609ABG-40R |

R1Q3A3636/R1Q3A3618/R1Q3A3609

General Description

Power-up and Initialization Sequence

The following supply voltage application sequence is recommended: V

SS

, V

DD

, V

DDQ

, V

REF

then V

IN

.

After the stable power, there are three possible sequences.

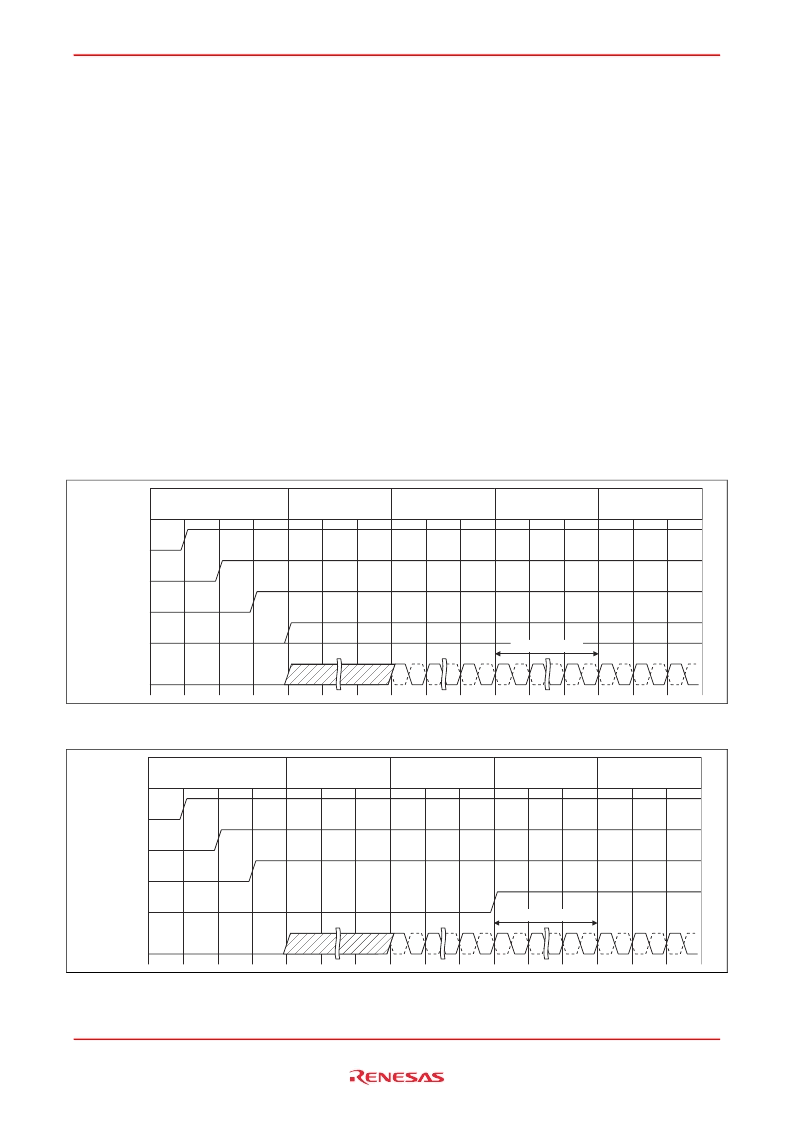

1. Sequence when DLL disable (/DOFF pin fixed low)

Just after the stable power and clock (K, /K, C, /C), 1024 NOP cycles (min.) are required for all operations,

including JTAG functions, to become normal.

2a. Sequence controlled by /DOFF pin when DLL enable Just after the stable power and clock (K, /K, C, /C), take

/DOFF to be high.

The additional 1024 NOP cycles (min.) are required to lock the DLL and for all operations to become normal.

2b. Sequence controlled by Clock (/DOFF pin fixed high) when DLL enable If /DOFF pin is fixed high with

unstable clock, the clock (K, /K, C, /C) must be stopped for 30ns (min.).

During stop clock stage, C pin must tie low for 30 ns (min.). C, /C, K and /K cannot remain V

REF

level.

The additional 1024 NOP cycles (min.) are required to lock the DLL and for all operations to become normal.

Notes: 1. After K or C clock is stopped, clock recovery cycles (1024 NOP cycles (min.)) are required for read/write

operations to become normal.

2. When DLL is enable and the operating frequency is changed, DLL reset should be required again. After DLL

reset again, the 1024 NOP cycles (min.) are needed to lock the DLL.

1. Sequence when DLL disable (/DOFF pin fixed low)

Status

Power Up

Unstable

Clock Stage

Stable

Clock Stage

NOP Stage

Normal

Operation

V

DD

C, /C, K, /K

V

DDQ

V

REF

V

IN

1024cycle min.

2a. Sequence controlled by /DOFF pin when DLL enable

Status

Power Up

Unstable

Clock Stage

Stable

Clock Stage

NOP & DLL

Locking Stage

Normal

Operation

V

DD

C, /C, K, /K

1024cycle min.

V

DDQ

V

REF

/DOFF

REJ03C0295-0003 Rev.0.03 Jul. 31, 2007

Page 6 of 24

相关PDF资料 |

PDF描述 |

|---|---|

| R1Q3A3609ABG-50R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3609ABG-60R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618 | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-30R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-33R | 36-Mbit QDR™II SRAM 4-word Burst |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R1Q3A3609ABG40RB0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609ABG40RS0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609ABG40RT0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609ABG-50R | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3609ABG50RB0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

发布紧急采购,3分钟左右您将得到回复。