- 您现在的位置:买卖IC网 > PDF目录69313 > R5F3650KNFB MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | R5F3650KNFB |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | MICROCONTROLLER, PQFP100 |

| 封装: | 14 X 14 MM, 0.50 MM PITCH, LQFP-100 |

| 文件页数: | 13/81页 |

| 文件大小: | 879K |

| 代理商: | R5F3650KNFB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页

111

4317K–AVR–03/2013

AT90PWM2/3/2B/3B

15.5

Input Capture Unit

The Timer/Counter incorporates an Input Capture unit that can capture external events and give

them a time-stamp indicating time of occurrence. The external signal indicating an event, or mul-

tiple events, can be applied via the ICPn pin or alternatively, via the analog-comparator unit. The

time-stamps can then be used to calculate frequency, duty-cycle, and other features of the sig-

nal applied. Alternatively the time-stamps can be used for creating a log of the events.

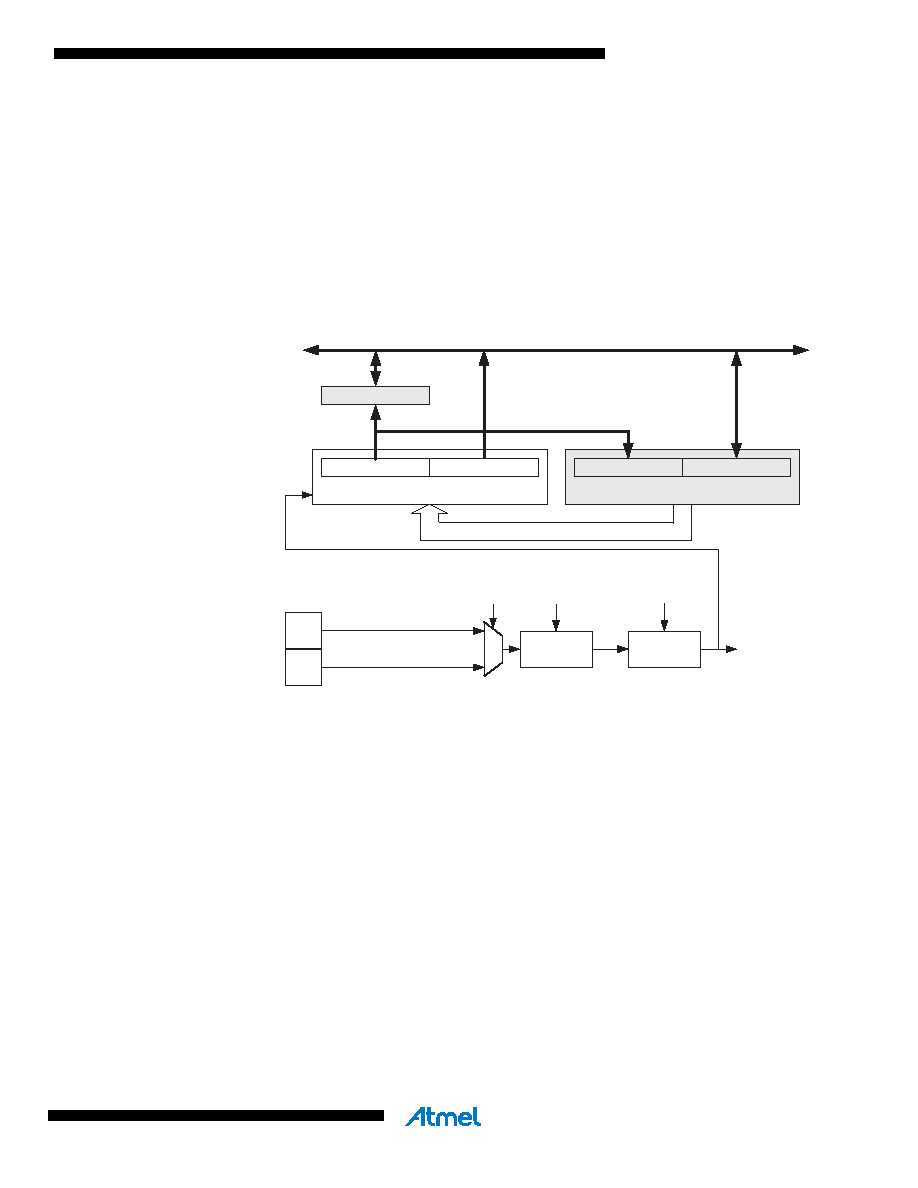

The Input Capture unit is illustrated by the block diagram shown in Figure 15-3. The elements of

the block diagram that are not directly a part of the Input Capture unit are gray shaded. The

small “n” in register and bit names indicates the Timer/Counter number.

Figure 15-3. Input Capture Unit Block Diagram

When a change of the logic level (an event) occurs on the Input Capture pin (ICPn), alternatively

on the Analog Comparator output (ACO), and this change confirms to the setting of the edge

detector, a capture will be triggered. When a capture is triggered, the 16-bit value of the counter

(TCNTn) is written to the Input Capture Register (ICRn). The Input Capture Flag (ICFn) is set at

the same system clock as the TCNTn value is copied into ICRn Register. If enabled (ICIEn = 1),

the Input Capture Flag generates an Input Capture interrupt. The ICFn Flag is automatically

cleared when the interrupt is executed. Alternatively the ICFn Flag can be cleared by software

by writing a logical one to its I/O bit location.

Reading the 16-bit value in the Input Capture Register (ICRn) is done by first reading the low

byte (ICRnL) and then the high byte (ICRnH). When the low byte is read the high byte is copied

into the high byte temporary register (TEMP). When the CPU reads the ICRnH I/O location it will

access the TEMP Register.

The ICRn Register can only be written when using a Waveform Generation mode that utilizes

the ICRn Register for defining the counter’s TOP value. In these cases the Waveform Genera-

tion mode (WGMn3:0) bits must be set before the TOP value can be written to the ICRn

Register. When writing the ICRn Register the high byte must be written to the ICRnH I/O location

before the low byte is written to ICRnL.

ICFn (Int.Req.)

WRITE

ICRn (16-bit Register)

ICRnH (8-bit)

Noise

Canceler

ICPnB

Edge

Detector

TEMP (8-bit)

DATA BUS (8-bit)

ICRnL (8-bit)

TCNTn (16-bit Counter)

TCNTnH (8-bit)

TCNTnL (8-bit)

ICPSEL1

ICNC

ICES

ICPnA

相关PDF资料 |

PDF描述 |

|---|---|

| R5F3650NNFB | MICROCONTROLLER, PQFP100 |

| R5F36B3ENNP | 16-BIT, FLASH, 16 MHz, MICROCONTROLLER, PQCC64 |

| R5F36CAKNFA | 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, PQFP100 |

| R5F36CAKNFB | 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, PQFP100 |

| R5F36CA6DFA | 16-BIT, FLASH, 32 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R5F3650KNFB#U0 | 功能描述:MCU 4KB FLASH 384/16K 100-LQFP RoHS:是 类别:集成电路 (IC) >> 嵌入式 - 微控制器, 系列:M16C™ M16C/60/65 标准包装:96 系列:PIC® 16F 核心处理器:PIC 芯体尺寸:8-位 速度:20MHz 连通性:I²C,SPI 外围设备:欠压检测/复位,POR,PWM,WDT 输入/输出数:11 程序存储器容量:3.5KB(2K x 14) 程序存储器类型:闪存 EEPROM 大小:- RAM 容量:128 x 8 电压 - 电源 (Vcc/Vdd):2.3 V ~ 5.5 V 数据转换器:A/D 8x10b 振荡器型:内部 工作温度:-40°C ~ 125°C 封装/外壳:14-TSSOP(0.173",4.40mm 宽) 包装:管件 |

| R5F3650MCDFA | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:televisions, household appliances, office equipment, communication devices |

| R5F3650MCDFB | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:televisions, household appliances, office equipment, communication devices |

| R5F3650MCNFA | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:televisions, household appliances, office equipment, communication devices |

| R5F3650MCNFB | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:televisions, household appliances, office equipment, communication devices |

发布紧急采购,3分钟左右您将得到回复。