- 您现在的位置:买卖IC网 > PDF目录378123 > R8820LV (Electronic Theatre Controls, Inc.) 16-BIT RISC MICROCONTROLLER PDF资料下载

参数资料

| 型号: | R8820LV |

| 厂商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 16-BIT RISC MICROCONTROLLER |

| 中文描述: | 16位RISC微控制器 |

| 文件页数: | 10/98页 |

| 文件大小: | 1000K |

| 代理商: | R8820LV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页

R DC

RISC DSP Controller

R8820LV

RDC Semiconductor Co.

Rev:1.0

Subject to change without notice

10

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

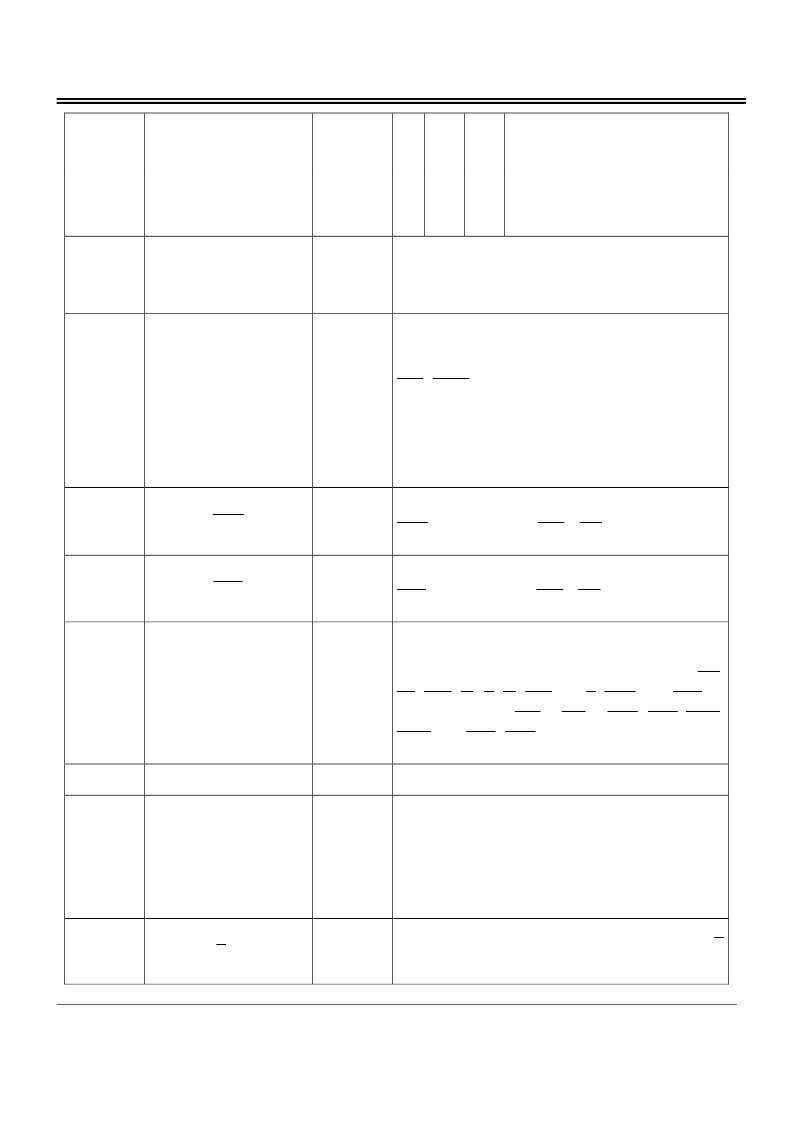

Interrupt acknowledge

Read data from I/O

Write data to I/O

Halt

Instruction fetch

Read data from memory

Write data to memory

Passive

19

20

22

23-37

39, 40

A19/PIO9

A18/PIO8

A17/PIO7

A16-A2

A1 , A0

Output/Input

Address bus. Non-multiplex memory or I/O address. The A

bus is one-half of a CLKOUTA period earlier than the AD

bus. These pins are high-impedance during bus hold or reset.

78,80,82,84,8

6,88

91,94

79,81,83,85,8

7,90

93,95

AD0-AD7

AD8-AD15

Input/Output

The multiplexed address and data bus for memory or I/O

accessing. The address is present during the t1 clock phase,

and the data bus phase is in t2-t4 cycle.

The address phase of the AD bus can be disabled when the

BHE

/ADEN pin with external pull-Low resister during

reset.

The AD bus is in high-impedance state during bus hold or

reset condition and this bus also be used to load system

configuration information (with pull-up or pull-Low

resister) into the RESCON register when the reset input

from low go high.

Write high byte. This pin indicates the high byte data (AD15-

AD8) on the bus is to be written to a memory or I/O device.

WHB is the logic OR of BHE , WR and AD0 inverting.

This pin is floating during reset or bus hold.

Write low byte. This pin indicates the low byte data (AD7-

AD0) on the bus is to be written to a memory or I/O device.

WLB is the logic OR of

BHE

, WR and AD0.

This pin is floating during reset or bus hold.

Bus hold acknowledge. Active high. The microcontroller will

issue a HLDA in response to a HOLD request by external bus

master at the end of T4 or Ti. When the microcontroller is in

hold status (HLDA is high), the AD15-AD0, A19-A0,WR ,

RD

,DEN ,S -S ,S ,

BHE

, DT/

R

, WHB and WLB are

floating, and the UCS, LCS,

0

MCS and

3

PCS -

0

PCS will be drive high. After HOLD is

detected as being low, the microcontroller will lower HLDA.

Bus Hold request. Active high. This pin indicates that another

bus master is requesting the local bus.

Synchronous ready. This pin performs the microcontroller

that the address memory space or I/O device will complete a

data transfer. The SRDY pin accepts a falling edge that is

asynchronous to CLKOUTA and is active high. SRDY is

accomplished by elimination of the one-half clock period

required to internally synchronize ARDY. Tie SRDY high the

microcontroller is always assert in the ready condition. If the

SRDY is not used, tie this pin low to yield control to ARDY.

Data transmit or receive. This pin indicates the direction of

data flow through an external data-bus transceiver. DT/

R

low, the microcontroller receives data. When DT/R is asserted

high, the microcontroller writes data to the data bus.

42

WHB

Output

43

WLB

Output

44

HLDA

Output

6

PCS -

5

PCS ,

3

MCS -

45

HOLD

Input

46

SRDY/PIO6

Input/Output

48

DT/

R

/

PIO4

Output/Input

相关PDF资料 |

PDF描述 |

|---|---|

| RA258 | Silicon Rectifier Button-Cells |

| RA2505 | Silicon Rectifier Button-Cells |

| RB5P0010M | Video Interface ICs for TFT-LCDs |

| RB5P0020M | Video Interface ICs for TFT-LCDs |

| RB5P0050M | Video Interface ICs for TFT-LCDs |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R8821 | 制造商:RDC 制造商全称:RDC 功能描述:16-BIT RISC MICROCONTROLLER |

| R8822 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:RDC 16 Bit RISC MICRO-CONTROLLER |

| R8822I | 制造商:RDC 制造商全称:RDC 功能描述:16-BIT RISC MICROCONTROLLER |

| R8830 | 制造商:RDC 制造商全称:RDC 功能描述:16-BIT RISC MICROCONTROLLER |

| R8830I | 制造商:RDC 制造商全称:RDC 功能描述:16-BIT RISC MICROCONTROLLER |

发布紧急采购,3分钟左右您将得到回复。