- 您现在的位置:买卖IC网 > PDF目录192180 > RD-19240FS-200 (DATA DEVICE CORP) SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, PQFP52 PDF资料下载

参数资料

| 型号: | RD-19240FS-200 |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 位置变换器 |

| 英文描述: | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, PQFP52 |

| 封装: | 10 X 10 MM, PLASTIC, MQFP-52 |

| 文件页数: | 4/19页 |

| 文件大小: | 432K |

| 代理商: | RD-19240FS-200 |

12

Data Device Corporation

www.ddc-web.com

RD-19240

F-02/09-0

resolution of the parallel data outputs may be changed any

time after the encoder resolution is latched (see FIGURE

15).

When in A_QUAD_B mode, the resolution of the parallel data

can be changed to a resolution equal to or greater than the

A_QUAD_B resolution setting only. For example if the

A_QUAD_B mode is active and the resolution is set to 12 bits,

the resolution of the parallel programmed data can be changed

from 12 to 14 bits by using D0 & D1. If 10-bit mode is required for

the parallel data, the A_QUAD_B resolution must also be pro-

grammed to 10 bits.

Note: The encoder resolution must be less than or equal to the

resolution of the parallel data outputs. Refer to FIGURE 17.

The timing of the A, B and ZIP (or North Reference Pole [NRP])

output

is

dependent

on

the

rate

of

change

of

the

synchro/resolver position (rps or degrees per second) and the

INTERNAL ENCODER EMULATION

The RD-19240 can be programmed to encoder emulation

mode by toggling the A_QUAD_B input to a logic 0. The U/B

output pin becomes B (LSB XOR LSB + 1). The A (LSB + 1)

and B output signals can be used in control systems that are

designed to interface with incremental optical encoders. To

enable the Zero Index pulse, ZIP_EN should be tied to a

logic 0.

An example circuit to create a low going edge of A_QUAD_B is

depicted in FIGURE 16. If the power supply takes longer than

50ms to start up then the time constant of 50ms set in FIGURE

16 will require being extended. Alternatively a system logic reset

signal or internally generated logic ‘load’ pulse can be generated

to latch in the encoder resolution.

The resolution of the incremental outputs is latched from the

D0 and D1 inputs on the low going edge of A_QUAD_B. The

RD-19240

1 MSB

2

3

4

9

10

11

12

13

14 LSB

B

1

0

1

2

1

4

A

5

6

7

8

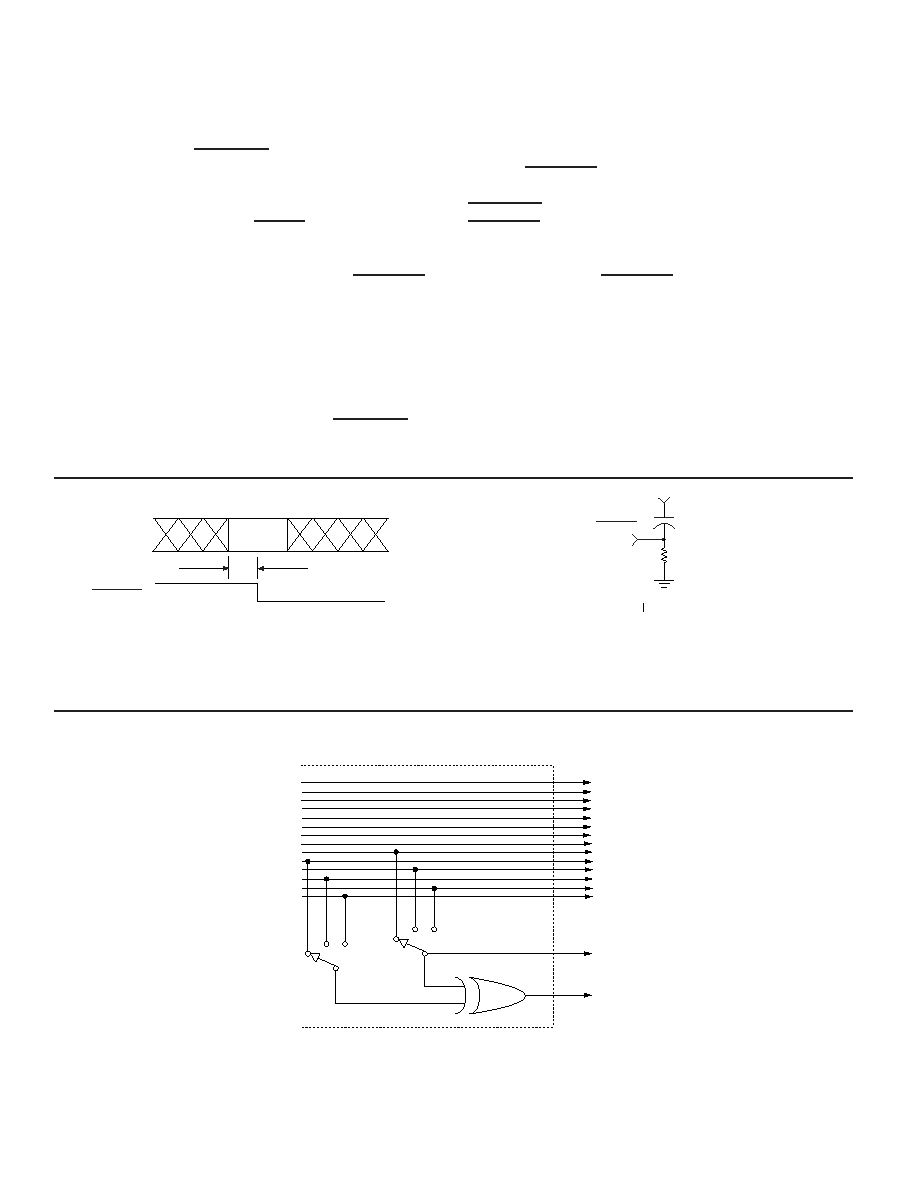

FIGURE 17. INCREMENTAL ENCODER EMULATION RESOLUTION CONTROL

DATA

VALID

50 nsec

D0/D1

A QUAD B

FIGURE 15. TIMING FOR INCREMENTAL ENCODER

EMULATION RESOLUTION CONTROL

A quad B

C

+5V

R

~

= RC

(i.e., 50ms = 50kohms x 1f)

FIGURE 16. EXAMPLE CIRCUIT FOR A QUAD B

RESET

相关PDF资料 |

PDF描述 |

|---|---|

| RD13UMB | 13 V, 0.15 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| RD18UMB3 | 18 V, 0.15 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| RD7.5UMB1 | 7.5 V, 0.15 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE |

| RD15JSAB | 15 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-34 |

| RD5.6JSAB1 | 5.6 V, 0.4 W, SILICON, UNIDIRECTIONAL VOLTAGE REGULATOR DIODE, DO-34 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RD1-9320 | 制造商:STMicroelectronics 功能描述:MPU DEMO-BOARD |

| RD1950MPXM2010GS | 制造商:Freescale Semiconductor 功能描述:WATER LEVEL REFERENCE DESIGN - Bulk |

| RD1986MMA2260D | 功能描述:加速传感器开发工具 TRIAX REF DSGN 3-AXIS FOR MMA2260D RoHS:否 制造商:Murata 工具用于评估:SCA3100-D04 加速:2 g 传感轴:Triple Axis 接口类型:SPI 工作电压:3.3 V |

| RD1986MMA6260Q | 功能描述:加速传感器开发工具 TRIAX REF DSGN 3-AXIS FOR NMA6260Q RoHS:否 制造商:Murata 工具用于评估:SCA3100-D04 加速:2 g 传感轴:Triple Axis 接口类型:SPI 工作电压:3.3 V |

| RD1A-12S | 制造商:World Products 功能描述: |

发布紧急采购,3分钟左右您将得到回复。