- 您现在的位置:买卖IC网 > PDF目录230914 > RDC-632-A-H-3-R (DATA DEVICE CORP) SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP27 PDF资料下载

参数资料

| 型号: | RDC-632-A-H-3-R |

| 厂商: | DATA DEVICE CORP |

| 元件分类: | 位置变换器 |

| 英文描述: | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP27 |

| 封装: | 3.125 X 2.625 INCH, 0.430 INCH HEIGHT, MODULE-28/27 |

| 文件页数: | 3/4页 |

| 文件大小: | 464K |

| 代理商: | RDC-632-A-H-3-R |

Data changes on the leading edge of the CB pulse, and data can

be transferred 0.5 sec after the leading edge.

The simplest method of interfacing with a computer is to transfer

data at a fixed time interval after the Inhibit is applied. The con-

verter will ignore an Inhibit during the “busy” interval until that

interval is over. Timing is as follows: (a) apply the Inhibit, (b) wait

0.5 sec, (c) transfer the data, (d) release the Inhibit. The Inhibit

line has no effect on converter tracking.

SIGNAL INPUTS

To prevent damage to the inputs, the maximum steady-state volt-

age should not exceed the specified input voltage by more than

30%.

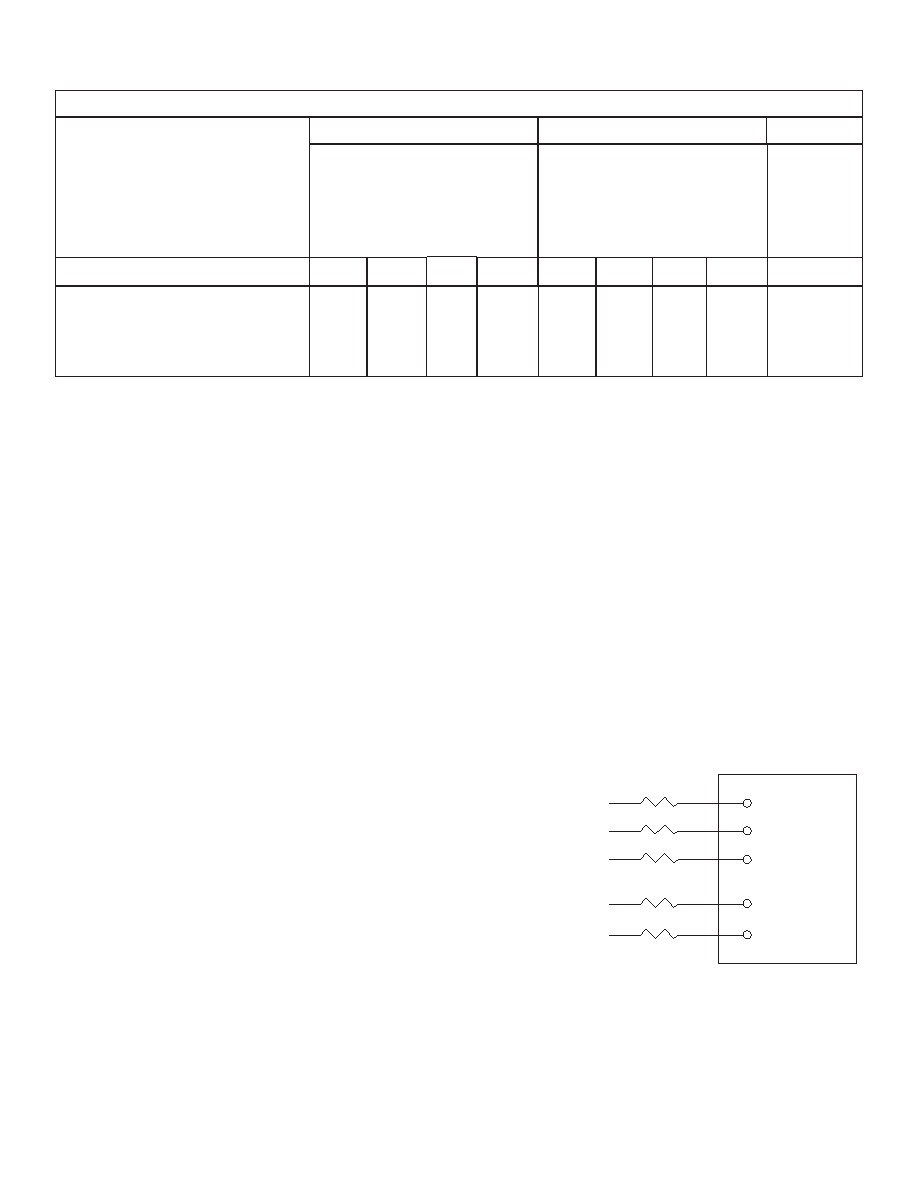

ACCOMMODATING NON-STANDARD INPUT

VOLTAGES (A ONLY)

The signal and reference input levels can be resistively scaled to

accommodate non-standard voltages, see FIGURE 3. Select a

converter that is the next lower standard voltage, and the voltage

is then scaled up by using resistors in series with the synchro

and/or reference inputs.

For a synchro input (SDC), a resistor R

SIG

is added in series

with S1, S2 and S3 which is determined as follows:

R

SIG = 1.1k (New L-L Voltage – Standard Unit L-L Voltage)

That is, 1.1k for each volt above the design voltage level of the

standard unit.

Example: An SDC-634A-L (11.8 V) is to be used at 50 V L-L.

R

SIG = 1.1k (50 – 11.8) = 42.2k

The closest available high grade resistor with a low temperature

coefficient of resistance should be used, and the three resistors

should be as closely matched to each other as possible. In gen-

eral, a 0.1% difference will introduce 1.7 arc minutes of addition-

al error due to the effect on SIN/COS ratio relationship.

The ABSOLUTE value of the resistor is not critical.

In the case of the RESOLVER version (RDC), the equation is:

R

SIG = 2.2k (New L-L Voltage – Standard Unit L-L Voltage)

The calculated resistors are connected in series with S1 and S2

respectively. Note only two resistors are required. The required

resistance matching and its effect on accuracy, is the same as for

a synchro input, see FIGURE 3. The Reference Voltage is treat-

ed in the same manner, but the value is not critical.

RREF = 2.8k (New Reference – Standard Reference)

For this use a 10% tolerance resistor is adequate.

3

UNITS

Hz

1/s

rps

°/s2

msec

60 HZ

47 - 1,000

15

1,100

0.1

7,600

33

16.3

28.5

24

370

500

10

12

14

16

10

12

14

16

7.1

6

93

600

1.8

1.5

23

900

0.45

0.37

5.8

2,200

192

160

17,000

90

48

40

4,220

100

12

10

1,050

140

3

2.5

260

320

400 HZ

360 - 1,000 (ST to 5,000)

100

48,000

1

48,000

220

110

RESOLUTION

Bandwidth (non F carrier)

Carrier Frequency Range

Bandwidth (Closed Loop)

Ka

A1

A2

A

B

Tracking Rate (rps)

Typical

Minimum

Acceleration (1 LSB lag)

Settling Time (179° step, max)

TABLE 2. SDC-630/632/634 A/ST DYNAMIC CHARACTERISTICS

{

NONSTANDARD

LINE-TO-LINE

LEVEL

SDC-630A

NONSTANDARD

REFERENCE

LEVEL

R

S1

S2

S3

R

SIG

REF

SIG

FIGURE 3. SDC-630/632/634 A/ST NON-STANDARD

INPUT LEVEL SCALING

相关PDF资料 |

PDF描述 |

|---|---|

| RDC-632-L-1 | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DMA27 |

| RDC-19229-423W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, CQCC44 |

| RDC-636-A-H-1-R | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DMA27 |

| RD-14595D1-442Y | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

| RD-14595D1-384W | SYNCHRO OR RESOLVER TO DIGITAL CONVERTER, DIP36 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RDC-632-A-L-1-R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Resolver-to-Digital Converter |

| RDC-632-A-L-3-R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Resolver-to-Digital Converter |

| RDC-632-ST-H-1-R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Resolver-to-Digital Converter |

| RDC-632-ST-H-3-R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Resolver-to-Digital Converter |

| RDC-632-ST-L-1-R | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Resolver-to-Digital Converter |

发布紧急采购,3分钟左右您将得到回复。