- 您现在的位置:买卖IC网 > PDF目录297328 > RV5C348A (RICOH COMPANY LTD) 4-WIRE SERIAL INTERFACE PDF资料下载

参数资料

| 型号: | RV5C348A |

| 厂商: | RICOH COMPANY LTD |

| 元件分类: | XO, clock |

| 英文描述: | 4-WIRE SERIAL INTERFACE |

| 中文描述: | 0 TIMER(S), REAL TIME CLOCK, PDSO10 |

| 封装: | 4 X 2.90 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, SSOP-10 |

| 文件页数: | 28/45页 |

| 文件大小: | 1276K |

| 代理商: | RV5C348A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页

Rx5C348A/B

Alarm and Periodic Interrupt

The Rx5C348A/B incorporates the alarm interrupt circuit and the periodic interrupt circuit that are configured to

generate alarm signals and periodic interrupt signals for output from the /INTR pin as described below.

(1) Alarm Interrupt Circuit

The alarm interrupt circuit is configured to generate alarm signals for output from the /INTR, which is driven low

(enabled) upon the occurrence of a match between current time read by the time counters (the day-of-week,

hour, and minute counters) and alarm time preset by the alarm registers (the Alarm_W registers intended for the

day-of-week, hour, and minute digit settings and the Alarm_D registers intended for the hour and minute digit

settings).

(2) Periodic Interrupt Circuit

The periodic interrupt circuit is configured to generate either clock pulses in the pulse mode or interrupt signals in

the level mode for output from the /INTR pin depending on the CT2, CT1, and CT0 bit settings in the control

register 1.

The above two types of interrupt signals are monitored by the flag bits (i.e. the WAFG, DAFG, and CTFG bits in

the Control Register 2) and enabled or disabled by the enable bits (i.e. the WALE, DALE, CT2, CT1, and CT0

bits in the Control Register 1) as listed in the table below.

Flag bits

Enable bits

Alarm_W

WAFG

(D1 at Address Fh)

WALE

(D7 at Address Eh)

Alarm_D

DAFG

(D0 at Address Fh)

DALE

(D6 at Address Eh)

Peridic interrupt

CTFG

(D2 at Address Fh)

CT2=CT1=CT0=0

(These bit setting of “0” disable the Periodic Interrupt)

(D2 to D0 at Address Eh)

*

At power-on, when the WALE, DALE, CT2, CT1, and CT0 bits are set to 0 in the Control Register 1,

the /INTR pin is driven high (disabled).

*

When two types of interrupt signals are output simultaneously from the /INTR pin, the output from the

/INTR pin becomes an OR waveform of their negative logic.

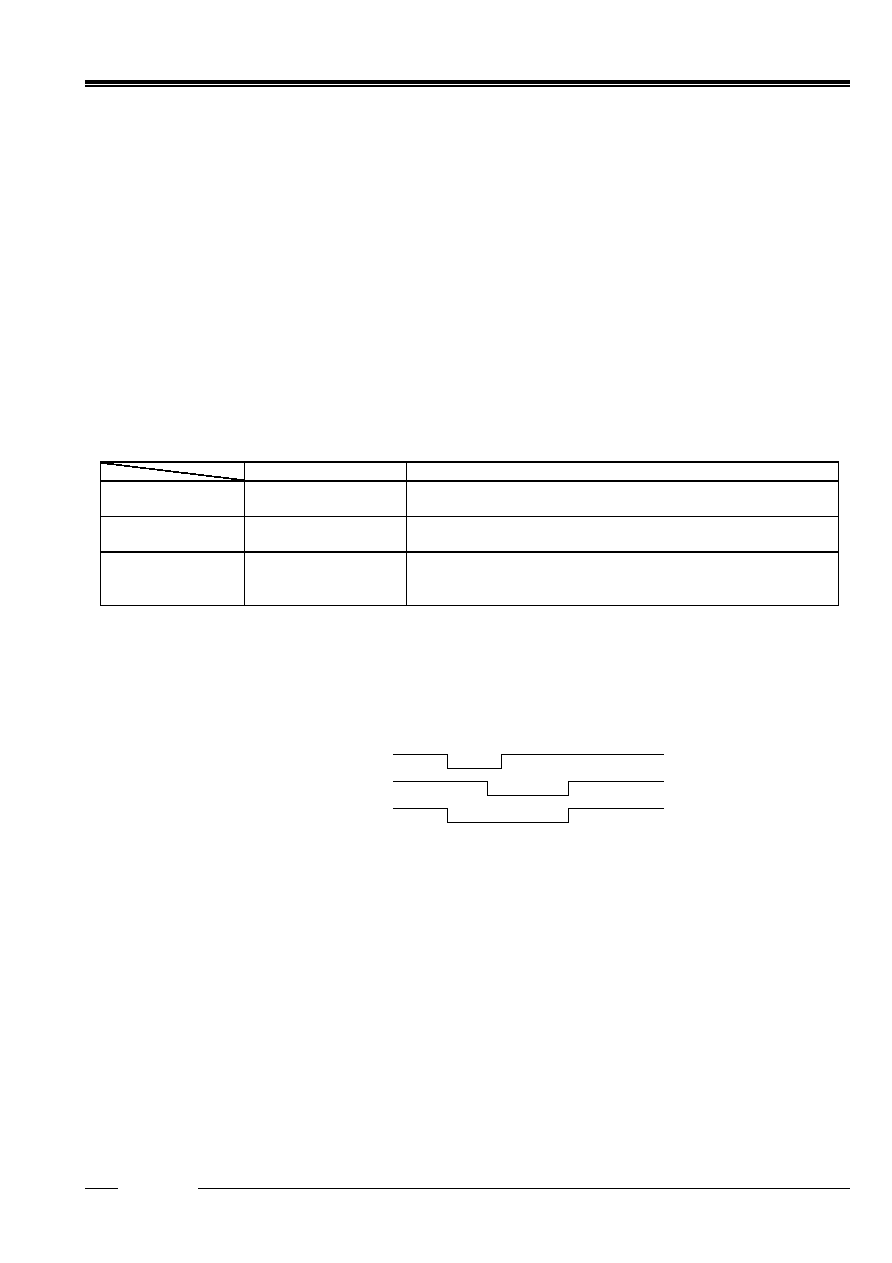

Example: Combined Output to /INTR Pin Under Control of

/ALARM_D and Periodic Interrupt

Periodic Interrupt

/INTR

/Alarm_D

In this event, which type of interrupt signal is output from the /INTR pin can be confirmed by reading the

DAFG, and CTFG bit settings in the Control Register 2.

Alarm Interrupt

The alarm interrupt circuit is controlled by the enable bits (i.e. the WALE and DALE bits in the Control Register 1)

and the flag bits (i.e. the WAFG and DAFG bits in the Control Register 2).

The enable bits can be used to

enable this circuit when set to 1 and to disable it when set to 0.

When intended for reading, the flag bits can be

used to monitor alarm interrupt signals.

When intended for writing, the flag bits will cause no event when set to

1 and will drive high (disable) the alarm interrupt circuit when set to 0.

The enable bits will not be affected even when the flag bits are set to 0.

In this event, therefore, the alarm

interrupt circuit will continue to function until it is driven low (enabled) upon the next occurrence of a match

between current time and preset alarm time.

12345

Rev.2.01

- 34 -

相关PDF资料 |

PDF描述 |

|---|---|

| RV5C348B | 4-WIRE SERIAL INTERFACE |

| RS9EM18M | RECTANGULAR ADAPTER |

| TDH25FJ1212 | RECTANGULAR ADAPTER |

| TDH25FJ4545K | RECTANGULAR ADAPTER |

| TDH25MJ12D | RECTANGULAR ADAPTER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RV5C348B | 制造商:RICOH 制造商全称:RICOH electronics devices division 功能描述:4-WIRE SERIAL INTERFACE REAL-TIME CLOCK ICs WITH VOLTAGE MONITORING FUNCTION |

| RV5C386A | 制造商:RICOH 制造商全称:RICOH electronics devices division 功能描述:I2C-bus Real-Time Clock ICs with Voltage Monitoring Function |

| RV5C386A_03 | 制造商:RICOH 制造商全称:RICOH electronics devices division 功能描述:I2C bus SERIAL INTERFACE REAL-TIME CLOCK IC WITH VOLTAGE MONITORING FUNCTION |

| RV5C386A-E2 | 制造商:RICOH 制造商全称:RICOH electronics devices division 功能描述:I2C-bus Real-Time Clock ICs with Voltage Monitoring Function |

| RV5C387A | 制造商:RICOH 制造商全称:RICOH electronics devices division 功能描述:I2C-bus Real-Time Clock ICs with Voltage Monitoring Function |

发布紧急采购,3分钟左右您将得到回复。