- 您现在的位置:买卖IC网 > PDF目录219504 > S-1172B50-E6T1U 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO6 PDF资料下载

参数资料

| 型号: | S-1172B50-E6T1U |

| 元件分类: | 固定正电压单路输出LDO稳压器 |

| 英文描述: | 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO6 |

| 封装: | HALOGEN FREE AND LEAD FREE, HSOP-6 |

| 文件页数: | 26/34页 |

| 文件大小: | 478K |

| 代理商: | S-1172B50-E6T1U |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页当前第26页第27页第28页第29页第30页第31页第32页第33页第34页

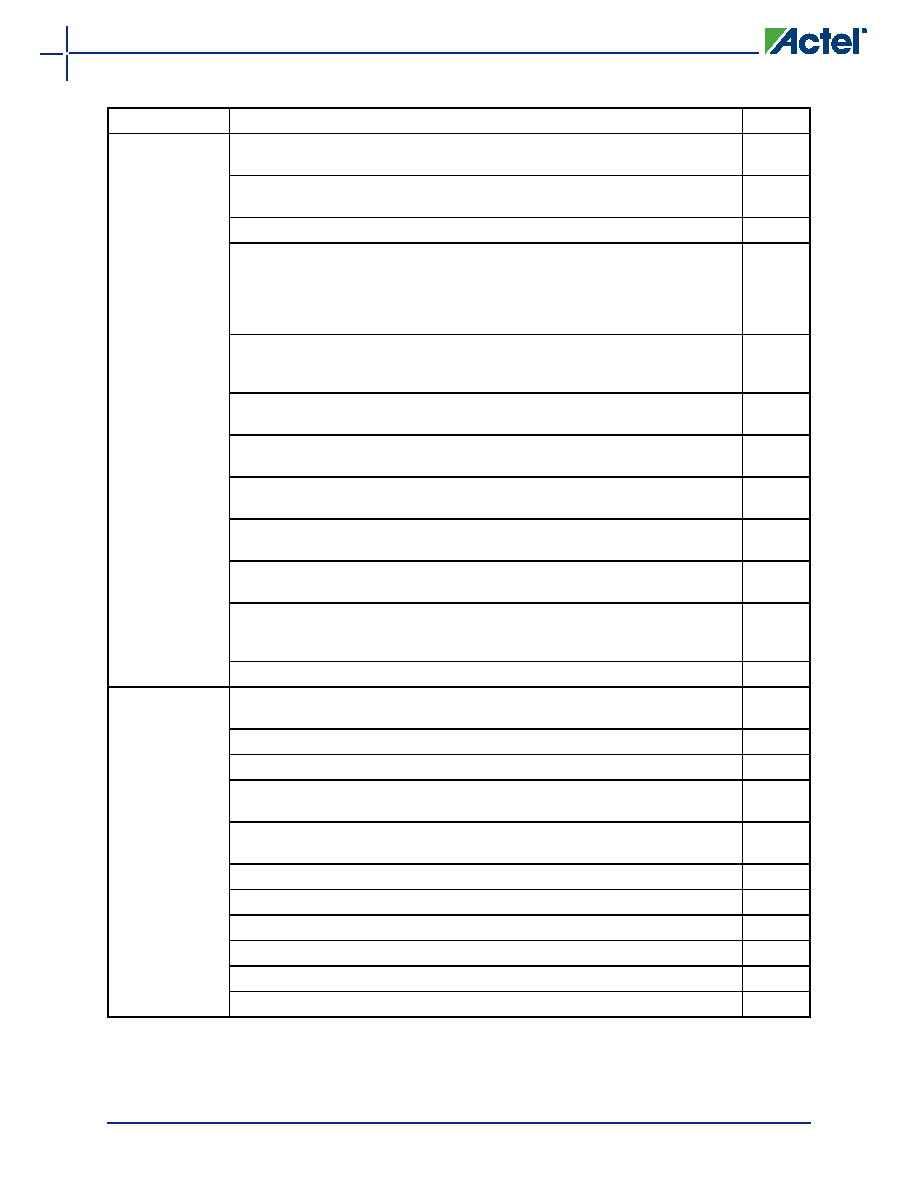

ProASIC3 DC and Switching Characteristics

2- 106

v1.3

Advance v0.7

(continued)

In EQ 3-2, 150 was changed to 110 and the result changed from 3.9 to 1.951.

3-5

Table 3-6 Temperature and Voltage Derating Factors for Timing Delays was

updated.

3-6

Table 3-5 Package Thermal Resistivities was updated.

3-5

Table 3-14 Summary of Maximum and Minimum DC Input and Output Levels

Applicable to Commercial and Industrial Conditions—Software Default Settings

(Advanced) and Table 3-17 Summary of Maximum and Minimum DC Input

Levels Applicable to Commercial and Industrial Conditions (Standard Plus) were

updated.

3-17 to

3-17

Table 3-20 Summary of I/O Timing Characteristics—Software Default Settings

(Advanced) and Table 3-21 Summary of I/O Timing Characteristics—Software

Default Settings (Standard Plus) were updated.

3-20 to

3-20

Table

3-11 Different

Components

Contributing

to

Dynamic

Power

Consumption in ProASIC3 Devices was updated.

3-9

Table 3-24 I/O Output Buffer Maximum Resistances1 (Advanced) and Table 3-

25 I/O Output Buffer Maximum Resistances1 (Standard Plus) were updated.

3-22 to

3-22

Table 3-17 Summary of Maximum and Minimum DC Input Levels Applicable to

Commercial and Industrial Conditions was updated.

3-18

Table 3-28 I/O Short Currents IOSH/IOSL (Advanced) and Table 3-29 I/O

Short Currents IOSH/IOSL (Standard Plus) were updated.

3-24 to

3-26

The note in Table 3-32 I/O Input Rise Time, Fall Time, and Related I/O

Reliability was updated.

3-27

Figure 3-33 Write Access After Write onto Same Address, Figure 3-34 Read

Access After Write onto Same Address, and Figure 3-35 Write Access After

Read onto Same Address are new.

3-82 to

3-84

Figure 3-43 Timing Diagram was updated.

3-96

Advance v0.5

(January 2006)

B-LVDS and M-LDVS are new I/O standards added to the datasheet.

N/A

The term flow-through was changed to pass-through.

N/A

Figure 2-7 Efficient Long-Line Resources was updated.

2-7

The footnotes in Figure 2-15 Clock Input Sources Including CLKBUF,

CLKBUF_LVDS/LVPECL, and CLKINT were updated.

2-16

The Delay Increments in the Programmable Delay Blocks specification in Figure

2-24 ProASIC3E CCC Options.

2-24

The "SRAM and FIFO" section was updated.

2-21

The "RESET" section was updated.

2-25

The "WCLK and RCLK" section was updated.

2-25

The "RESET" section was updated.

2-25

The "RESET" section was updated.

2-27

The "Introduction" of the "Advanced I/Os" section was updated.

2-28

Previous Version

Changes in Current Version (v1.3)

Page

相关PDF资料 |

PDF描述 |

|---|---|

| S-1172B50-U5T1U | 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO5 |

| S-1323B19NB-N8ETFU | 1.9 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1323B35NB-N8UTFU | 3.5 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1323B35PF-N8UTFU | 3.5 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1701B3024-M5T1U | 3 V FIXED POSITIVE LDO REGULATOR, 0.21 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S-1172B50-U5T1G | 功能描述:低压差稳压器 - LDO LINEAR LDO REG HI 70UA IQ 1000MA IOUT RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| S-1172B50-U5T1U | 功能描述:IC REG LINEAR 1A SOT89-5 制造商:ablic u.s.a. inc. 系列:* 包装:剪切带(CT) 零件状态:在售 电流 - 输出:1A 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:SOT-89-5/6 供应商器件封装:SOT-89-5 标准包装:1 |

| S1174-6W-SP | 制造商:Cooper Wiring Devices 功能描述: |

| S-1176-SP | 制造商:Molex 功能描述: |

| S-1177-SP | 制造商:Molex 功能描述: |

发布紧急采购,3分钟左右您将得到回复。