- 您现在的位置:买卖IC网 > PDF目录219504 > S-1172B50-E6T1U 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO6 PDF资料下载

参数资料

| 型号: | S-1172B50-E6T1U |

| 元件分类: | 固定正电压单路输出LDO稳压器 |

| 英文描述: | 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO6 |

| 封装: | HALOGEN FREE AND LEAD FREE, HSOP-6 |

| 文件页数: | 32/34页 |

| 文件大小: | 478K |

| 代理商: | S-1172B50-E6T1U |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页当前第32页第33页第34页

ProASIC3 DC and Switching Characteristics

2- 80

v1.3

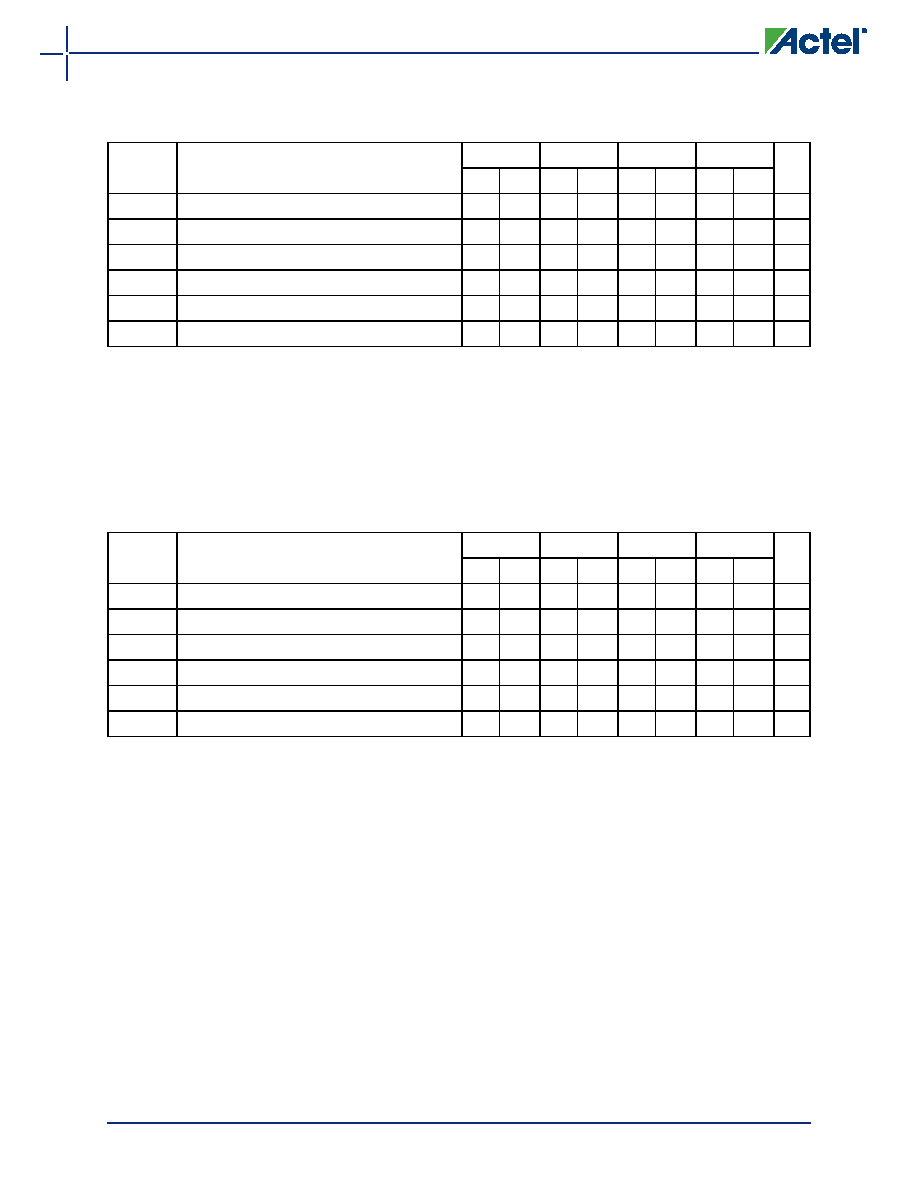

Table 2-100 A3P060 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

Parameter

Description

–2

–1

Std.

–F

Units

Min.1 Max.2 Min.1 Max.2 Min.1 Max.2 Min.1 Max.2

tRCKL

Input LOW Delay for Global Clock

0.71 0.93 0.81 1.05 0.95 1.24 1.14 1.49

ns

tRCKH

Input HIGH Delay for Global Clock

0.700.96 0.801.090.941.281.131.54

ns

tRCKMPWH Minimum Pulse Width HIGH for Global Clock

ns

tRCKMPWL Minimum Pulse Width LOW for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.26

0.29

0.34

0.41

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

Table 2-101 A3P125 Global Resource

Commercial-Case Conditions: TJ = 70°C, VCC = 1.425 V

Parameter

Description

–2

–1

Std.

–F

Units

Min.1 Max.2 Min.1 Max.2 Min.1 Max.2 Min.1 Max.2

tRCKL

Input LOW Delay for Global Clock

0.77 0.99 0.87 1.12 1.03 1.32 1.24 1.58

ns

tRCKH

Input HIGH Delay for Global Clock

0.761.02 0.871.161.021.371.231.64

ns

tRCKMPWH Minimum Pulse Width HIGH for Global Clock

ns

tRCKMPWL Minimum Pulse Width LOW for Global Clock

ns

tRCKSW

Maximum Skew for Global Clock

0.26

0.29

0.34

0.41

ns

FRMAX

Maximum Frequency for Global Clock

MHz

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential

element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element,

located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating

values.

相关PDF资料 |

PDF描述 |

|---|---|

| S-1172B50-U5T1U | 5 V FIXED POSITIVE LDO REGULATOR, 0.1 V DROPOUT, PDSO5 |

| S-1323B19NB-N8ETFU | 1.9 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1323B35NB-N8UTFU | 3.5 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1323B35PF-N8UTFU | 3.5 V FIXED POSITIVE LDO REGULATOR, 0.65 V DROPOUT, PDSO4 |

| S-1701B3024-M5T1U | 3 V FIXED POSITIVE LDO REGULATOR, 0.21 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S-1172B50-U5T1G | 功能描述:低压差稳压器 - LDO LINEAR LDO REG HI 70UA IQ 1000MA IOUT RoHS:否 制造商:Texas Instruments 最大输入电压:36 V 输出电压:1.4 V to 20.5 V 回动电压(最大值):307 mV 输出电流:1 A 负载调节:0.3 % 输出端数量: 输出类型:Fixed 最大工作温度:+ 125 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-20 |

| S-1172B50-U5T1U | 功能描述:IC REG LINEAR 1A SOT89-5 制造商:ablic u.s.a. inc. 系列:* 包装:剪切带(CT) 零件状态:在售 电流 - 输出:1A 工作温度:-40°C ~ 85°C(TA) 安装类型:表面贴装 封装/外壳:SOT-89-5/6 供应商器件封装:SOT-89-5 标准包装:1 |

| S1174-6W-SP | 制造商:Cooper Wiring Devices 功能描述: |

| S-1176-SP | 制造商:Molex 功能描述: |

| S-1177-SP | 制造商:Molex 功能描述: |

发布紧急采购,3分钟左右您将得到回复。