- 您现在的位置:买卖IC网 > PDF目录219503 > S-812C30AY-BG 3 V FIXED POSITIVE LDO REGULATOR, 0.41 V DROPOUT, PBCY3 PDF资料下载

参数资料

| 型号: | S-812C30AY-BG |

| 元件分类: | 固定正电压单路输出LDO稳压器 |

| 英文描述: | 3 V FIXED POSITIVE LDO REGULATOR, 0.41 V DROPOUT, PBCY3 |

| 封装: | LEAD FREE, TO-92, 3 PIN |

| 文件页数: | 3/39页 |

| 文件大小: | 690K |

| 代理商: | S-812C30AY-BG |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页

W946432AD

11

Burst Length

Read and write accesses to the DDR SDRAM are burst oriented, with the burst length being programmable,

as shown in Table 1: The burst length determines the maximum number of column locations that can be

accessed for a given READ or WRITE command. Burst lengths of 2, 4, locations are available for both the

sequential and the interleaved burst types.

When a READ or WRITE command is issued, a block of columns equal to the burst length is effectively

selected. All accesses for that burst take place with in this block, meaning that the burst will wrap within the

block if a boundary is reached. The block is uniquely selected by A1-A7 when the burst length is set to two,

by A2-A7 when the burst length is set to four and by A3-A7 when the burst length is set to eight. The

remaining address bit is used to select the starting location within the block. The programmed burst length

applies to both READ and WRITE bursts.

Burst Type

Accesses within a given burst may be programmed to be either sequential or interleaved; this is referred to

as the burst type and is selected by bit A3.

The ordering of accesses within a burst is determined by the burst length, the burst type and the starting

column address, as shown in Table 1:.

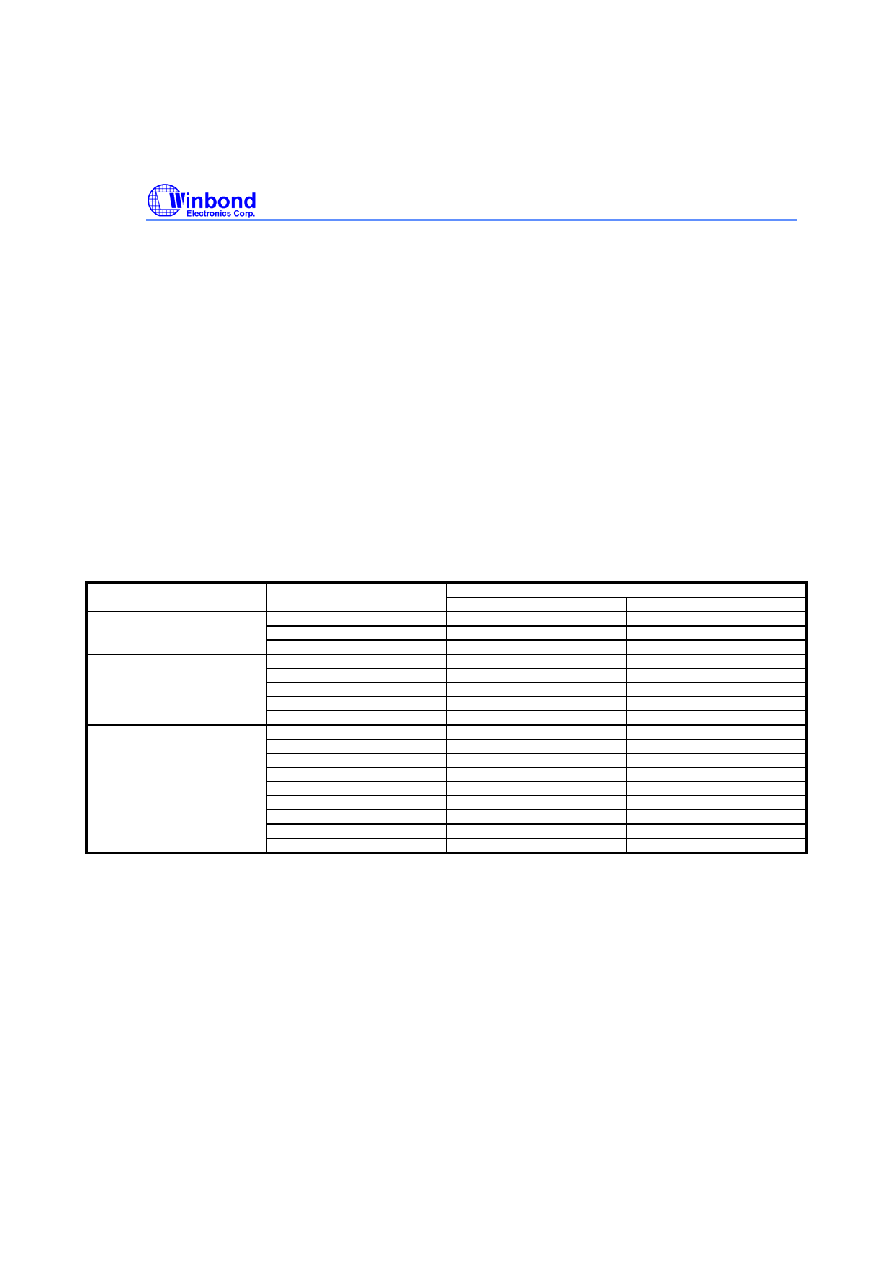

Table 1:BURST DEFINITION

Order of Accesses Within a Burst

Burst Length

Starting Column

Address:

Type = Sequential

Type = Interleaved

A0

0

0 - 1

2

1

1 – 0

A1

A0

0

0–1–2-3

0-1-2-3

0

1

1–2–3–0

1-0-3-2

1

0

2–3–0–1

2-3-0-1

4

1

3–0–1–2

3-2-1-0

A2

A1

A0

0

0-1-2-3-4-5-6-7

0

1

1-2-3-4-5-6-7-0

1-0-3-2-5-4-7-6

0

1

0

2-3-4-5-6-7-0-1

2-3-0-1-6-7-4-5

0

1

3-4-5-6-7-0-1-2

3-2-1-0-7-6-5-4

1

0

4-5-6-7-0-1-2-3

1

0

1

5-6-7-0-1-2-3-4

5-4-7-6-1-0-3-2

1

0

6-7-0-1-2-3-4-5

6-7-4-5-2-3-0-1

8

1

7-0-1-2-3-4-5-6

7-6-5-4-3-2-1-0

NOTE:

1. For a burst length of two, A1-A7 selects the two-data-element block; A0 selects

the first access within the block.

2. For a burst length of four, A2-A7 selects the four-data-element block; A0-A1

selects the first access within the block.

3. For a burst length of eight, A3-A7 selects the eight-data- element block; A0-A2

selects the first access within the block.

4. Whenever a boundary of the block is reached within a given sequence above, the

following access wraps within the block.

相关PDF资料 |

PDF描述 |

|---|---|

| S-812C30AY-ZG | 3 V FIXED POSITIVE LDO REGULATOR, 0.41 V DROPOUT, PBCY3 |

| S-812C30BPI-C4KTFGG | 3 V FIXED POSITIVE LDO REGULATOR, 0.41 V DROPOUT, PDSO6 |

| S-812C39AUA-C2T-T2G | 3.9 V FIXED POSITIVE LDO REGULATOR, 0.35 V DROPOUT, PSSO3 |

| S-812C39AY-BG | 3.9 V FIXED POSITIVE LDO REGULATOR, 0.35 V DROPOUT, PBCY3 |

| S-812C39BMC-C4T-T2G | 3.9 V FIXED POSITIVE LDO REGULATOR, 0.35 V DROPOUT, PDSO5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S-812C30AY-B-G | 制造商:Seiko Instruments Inc (SII) 功能描述:LDO Regulator Pos 3V 0.05A 3-Pin TO-92B Bulk |

| S-812C30AY-T-G | 制造商:Seiko Instruments Inc (SII) 功能描述:REG STD LIN FIX POS 3V 0.05A 3PIN TO-92A - Tape and Reel |

| S-812C30AY-X | 制造商:SII 制造商全称:Seiko Instruments Inc 功能描述:HIGH OPERATING VOLTAGE CMOS VOLTAGE REGULATOR |

| S-812C30AY-X-G | 制造商:SII 制造商全称:Seiko Instruments Inc 功能描述:HIGH OPERATING VOLTAGE CMOS VOLTAGE REGULATOR |

| S-812C30BMC-C4K-T2 | 制造商:SII 制造商全称:Seiko Instruments Inc 功能描述:HIGH OPERATING VOLTAGE CMOS VOLTAGE REGULATOR |

发布紧急采购,3分钟左右您将得到回复。