- 您现在的位置:买卖IC网 > PDF目录378687 > SC16C554BIB80 (NXP Semiconductors N.V.) 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs PDF资料下载

参数资料

| 型号: | SC16C554BIB80 |

| 厂商: | NXP Semiconductors N.V. |

| 元件分类: | 收发器 |

| 英文描述: | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs |

| 封装: | SC16C554BIB64<SOT314-2 (LQFP64)|<<http://www.nxp.com/packages/SOT314-2.html<1<week 36, 2004,;SC16C554BIB64<SOT314-2 (LQFP64)|<<http://www.nxp.com/packages/SOT314-2.html&l |

| 文件页数: | 17/58页 |

| 文件大小: | 1035K |

| 代理商: | SC16C554BIB80 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页

SC16C554B_554DB

All information provided in this document is subject to legal disclaimers.

NXP B.V. 2010. All rights reserved.

Product data sheet

Rev. 4 — 8 June 2010

17 of 58

NXP Semiconductors

SC16C554B/554DB

5 V, 3.3 V and 2.5 V quad UART, 5 Mbit/s (max.) with 16-byte FIFOs

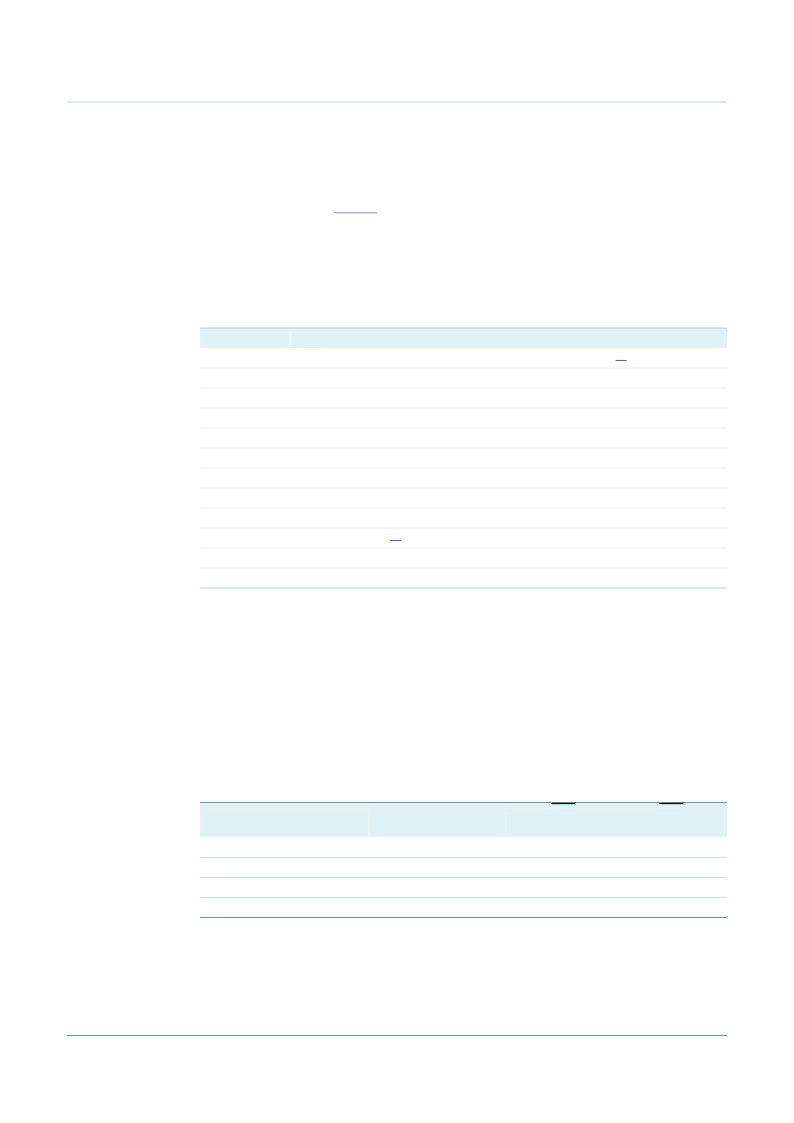

6.2 Internal registers

The SC16C554B/554DB provides 12 internal registers for monitoring and control. These

registers are shown in

Table 5

. These registers function as data holding registers

(THR/RHR), interrupt status and control registers (IER/ISR), a FIFO Control Register

(FCR), line status and control registers (LCR/LSR), modem status and control registers

(MCR/MSR), programmable data rate (clock) control registers (DLL/DLM), and a user

accessible Scratchpad Register (SPR). Register functions are more fully described in the

following paragraphs.

Table 5.

A2

General register set (THR/RHR, IER/ISR, MCR/MSR, FCR, LCR/LSR, SPR)

[1]

0

0

0

Receive Holding Register

0

0

1

Interrupt Enable Register

0

1

0

Interrupt Status Register

0

1

1

Line Control Register

1

0

0

Modem Control Register

1

0

1

Line Status Register

1

1

0

Modem Status Register

1

1

1

Scratchpad Register

Baud rate register set (DLL/DLM)

[2]

0

0

0

LSB of Divisor Latch

[1]

These registers are accessible only when LCR[7] is a logic 0.

[2]

These registers are accessible only when LCR[7] is a logic 1.

6.3 FIFO operation

The 16 byte transmit and receive data FIFOs are enabled by the FIFO Control Register

(FCR) bit 0. With SC16C554B devices, the user can set the receive trigger level, but not

the transmit trigger level. The receiver FIFO section includes a time-out function to ensure

data is delivered to the external CPU. An interrupt is generated whenever the Receive

Holding Register (RHR) has not been read following the loading of a character or the

receive trigger level has not been reached.

Table 6.

Selected trigger level

(characters)

1

4

8

14

Internal registers decoding

A0

Read mode

A1

Write mode

Transmit Holding Register

Interrupt Enable Register

FIFO Control Register

Line Control Register

Modem Control Register

n/a

n/a

Scratchpad Register

LSB of Divisor Latch

0

0

1

MSB of Divisor Latch

MSB of Divisor Latch

Flow control mechanism

INTn pin activation

Negate RTS

Assert RTS

1

4

8

14

4

8

12

14

1

4

8

10

相关PDF资料 |

PDF描述 |

|---|---|

| SC16C554BIBM | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs |

| SC16C554BIBS | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs |

| SC16C554DBIA68 | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs |

| SC16C554DBIB64 | 5 V, 3.3 V and 2.5 V quad UART, 5 Mbit-s (max.) with 16-byte FIFOs |

| SC16IS850LIBS | Single UART with I2C-bus-SPI interface, 128 bytes of transmit and receive FIFOs, IrDA SIR built-in support |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SC16C554BIB80,528 | 功能描述:UART 接口集成电路 4CH. UART 16B FIFO RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| SC16C554BIB80,551 | 功能描述:UART 接口集成电路 16CB 2.5V-5V 4CH RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| SC16C554BIB80,557 | 功能描述:UART 接口集成电路 16CB 2.5V-5V 4CH UART 16B FIFO RoHS:否 制造商:Texas Instruments 通道数量:2 数据速率:3 Mbps 电源电压-最大:3.6 V 电源电压-最小:2.7 V 电源电流:20 mA 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:LQFP-48 封装:Reel |

| SC16C554BIB80528 | 制造商:NXP Semiconductors 功能描述: |

| SC16C554BIB80557 | 制造商:Rochester Electronics LLC 功能描述: 制造商:NXP 功能描述: 制造商:NXP Semiconductors 功能描述: |

发布紧急采购,3分钟左右您将得到回复。