- 您现在的位置:买卖IC网 > PDF目录85256 > SC515846CPV (FREESCALE SEMICONDUCTOR INC) 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP112 PDF资料下载

参数资料

| 型号: | SC515846CPV |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP112 |

| 封装: | LQFP-112 |

| 文件页数: | 66/142页 |

| 文件大小: | 6464K |

| 代理商: | SC515846CPV |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页当前第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页

Device User Guide — 9S12DT128DGV2/D V02.15

Freescale Semiconductor

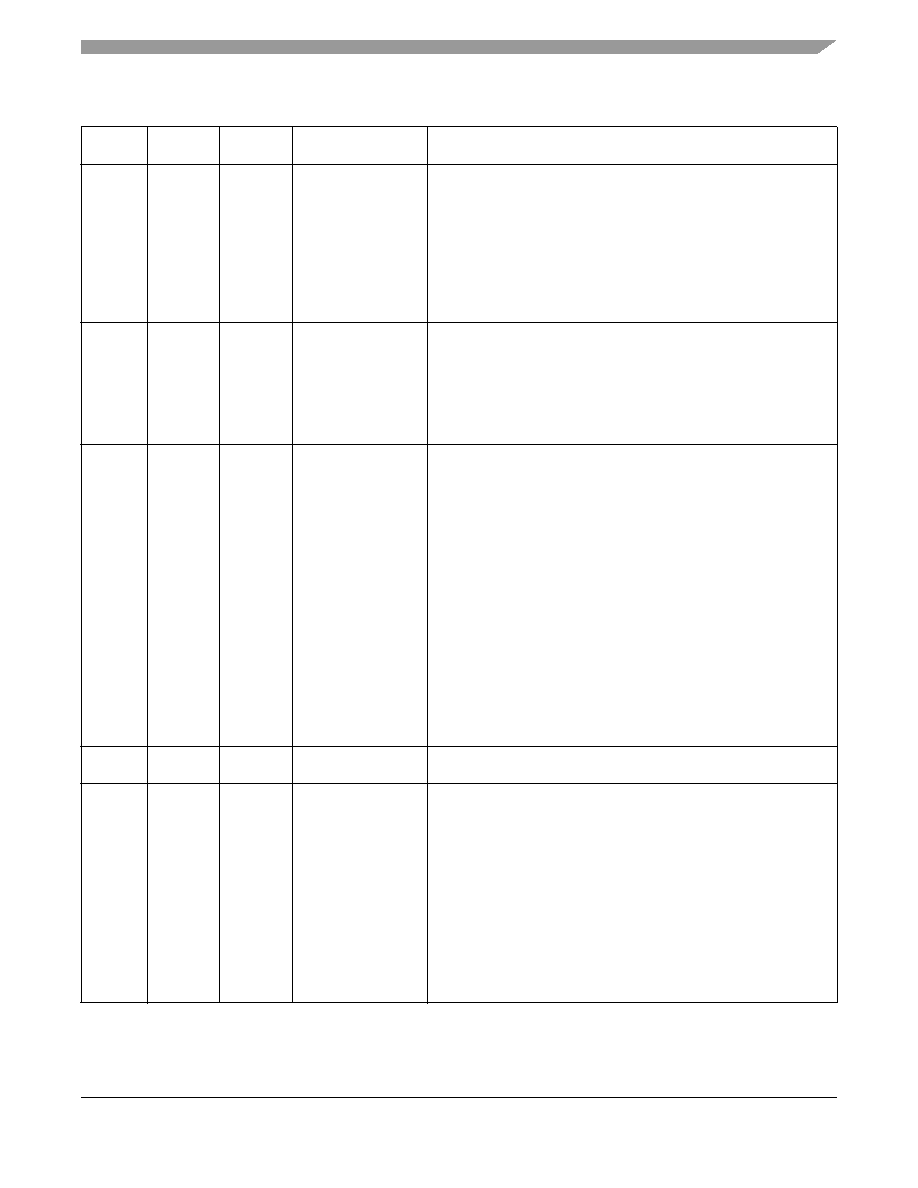

3

V02.02

08 Mar

2002

08 Mar

2002

Changed XCLKS to PE7 in Table 2-2

Updated device part numbers in Figure 2-1

Updated BDM clock in Figure 3-1

Removed SIM description in overview & nUPOSC spec in Table A-15

Updated electrical spec of VDD & VDDPLL (Table A-4), IOL/IOH

(Table A-6), CINS (Table A-9), CIN (Table A-6 & A-15),

Updated interrupt pulse timing variables in Table A-6

Updated device part numbers in Figure 2-1

Added document numbers on cover page and Table 0-2

V02.03

14 Mar

2002

14 Mar

2002

Cleaned up Fig. 1-1, 2-1

Updated Section 1.5 descriptions

Corrected PE assignment in Table 2-2, Fig. 2-5,6,7.

Corrected NVM sizes in Sections 16, 17

Added IREF spec for 1ATD in Table A-8

Added Blank Check in A.3.1.5 and Table A-11

Updated CRG spec in Table A-15

V02.04

16 Aug

2002

16 Aug

2002

Added:

Pull-up columns to signal table,

Example for PLL Filter calculation,

Thermal values for junction to board and package,

BGND pin pull-up

Part Order Information

Global Register Table

Chip Conguration Summary

Device specic info on CRG

Modied:

Reduced Wait and Run IDD values

Mode of Operation chapter

Changed leakage current for ADC inputs down to +-1uA

Minor modication of PLL frequency/ voltage gain values

Corrected:

Pin names/functions on 80 pin packages

Interrupt vector table enable register inconsistencies

PCB layout for 80QFP VREGEN position

V02.05

12 Sep

2002

12 Sep

2002

Corrected:

Register address mismatches in 1.5.1

V02.06

06 Nov

2002

06 Nov

2002

Removed document order no. from Revision History pages

Renamed "Preface" section to "Derivative Differences and

Document references". Added details for derivatives missing

CAN0/1/4, BDLC, IIC and/or Byteight

Added 2L40K mask set in section 1.6

Added OSC User Guide in Preface, “Document References”

Added oscillator clock connection to BDM in S12_CORE in g 3-1

Corrected several register and bit names in “Local Enable” column

of Table 5.1 Interrupt Vector Locations

Section HCS12 Core Block Description: mentioned alternate clock

of BDM to be equivalent to oscillator clock

Added new section: “Oscillator (OSC) Block Description”

Corrected in footnote of Table "PLL Characteristics": fOSC = 4MHz

Version

Number

Revision

Date

Effective

Date

Author

Description of Changes

相关PDF资料 |

PDF描述 |

|---|---|

| S3S12HN64J3CAA | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP80 |

| S3S12HN64J3VAA | 16-BIT, MROM, 25 MHz, MICROCONTROLLER, PQFP80 |

| SC103335VR400B | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA272 |

| SAH-XC2265N-40F40L | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP100 |

| SCN8032HCFA44 | 8-BIT, 7.5 MHz, MICROCONTROLLER, PQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SC515847 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| SC515848 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Device User Guide |

| SC515849 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:MC9S12DT128 Device User Guide V02.09 |

| SC516/WH | 制造商:CQR Security 功能描述:REED AND MAGNET HOUSING |

| SC51601FBR2 | 制造商:Motorola Inc 功能描述: |

发布紧急采购,3分钟左右您将得到回复。