- 您现在的位置:买卖IC网 > PDF目录98082 > SL28505ALC PROC SPECIFIC CLOCK GENERATOR, QCC64 PDF资料下载

参数资料

| 型号: | SL28505ALC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | PROC SPECIFIC CLOCK GENERATOR, QCC64 |

| 封装: | 9 X 9 MM, 0.50 MM PITCH, ROHS COMPLIANT, QFN-64 |

| 文件页数: | 12/28页 |

| 文件大小: | 312K |

| 代理商: | SL28505ALC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

SL28505

Rev 1.0 April 24, 2008

Page 2 of 28

Pin Definitions

Pin No.

Name

Type

Description

1

VSS_REF

GND

Ground for outputs.

2

XOUT

O, SE 14.318 MHz Crystal output.

3

XIN

I

14.318 MHz Crystal input.

4

VDD_REF

PWR

3.3V Power supply for outputs and also maintains SMBUS registers during

power-down.

5

REF0/FSC/TEST_SEL

I/O

3.3V tolerant input for CPU frequency selection/fixed 14.318 clock output.

Selects test mode if pulled to VIHFS_C when CK_PWRGD is asserted HIGH.

Refer to DC Electrical Specifications table for VILFS_C, VIMFS_C, VIHFS_C speci-

fications.

6

SDATA

I/O

SMBus compatible SDATA.

7

SCLK

I

SMBus compatible SCLOCK.

8

PCI0/CR#_A

I/O, SE 33 MHz clock/3.3V OE# Input mappable via I2C to control either SRC 0 or

SRC 2. Default PCI0

9

VDD_PCI

PWR

3.3V Power supply for PCI PLL.

10

PCI1/CR#_B

I/O, SE 33 MHz clock/3.3V OE# Input mappable via I2C to control either SRC 1 or

SRC 4. Default PCI1.

11

PCI2/TME

I/O, SE 3.3V tolerance input for overclocking enable pin 33 MHz clock.

Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifica-

tions.

12

PCI3/CFG0

I/O, SE,

PD

3.3V tolerant input for CPU frequency selection/33 MHz clock.

Refer to DC Electrical Specifications table for Vil_PCI3/CFG0 and

Vih_PCI3/CFG0 specifications.

13

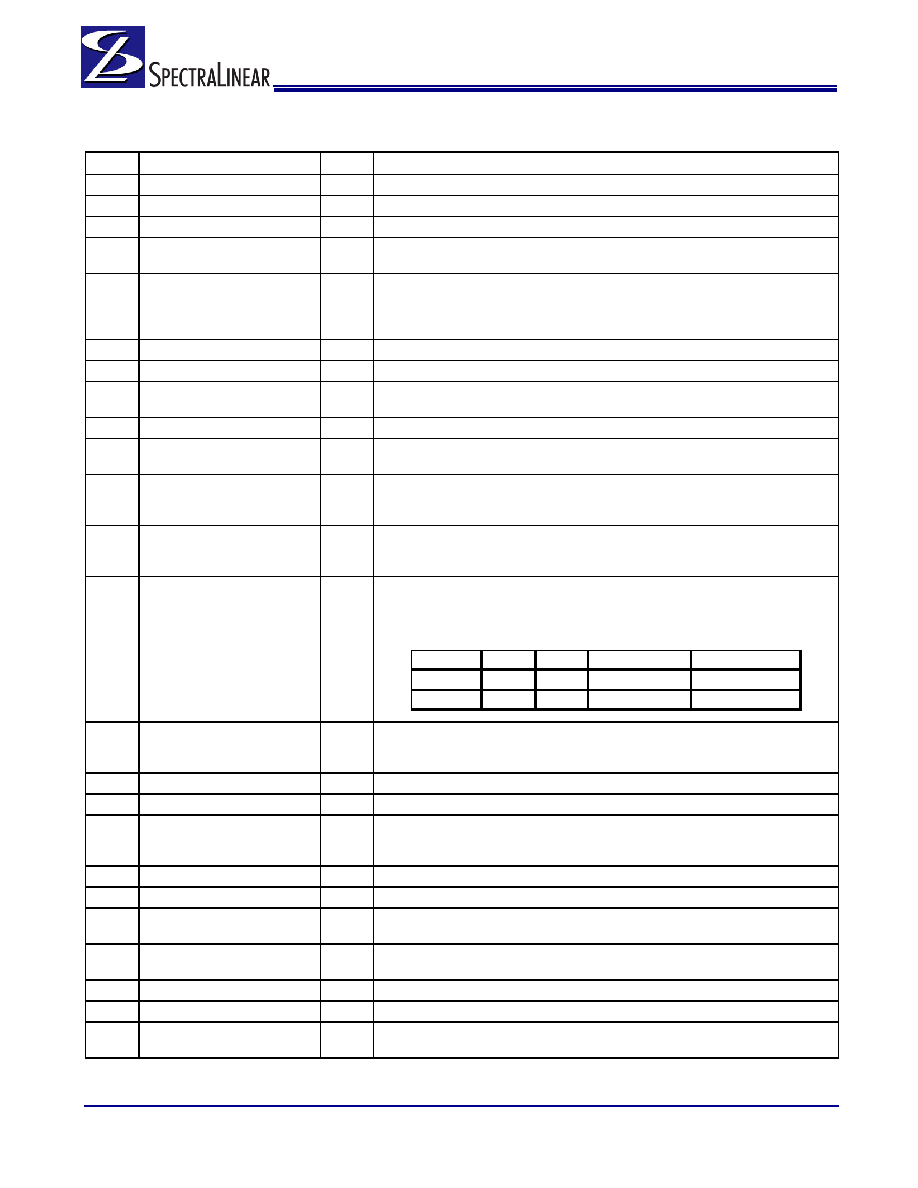

PCI4 / GCLK_SEL

I/O, SE 33 MHz clock output/3.3V-tolerant input for selecting graphic clock source on

pin 13, 14, 17and 18

Sampled on CKPWRGD assertion

14

PCIF0/ITP_EN

I/O, SE 3.3V LVTTL input to enable SRC8 or CPU2_ITP/33 MHz clock output.

(sampled on the CK_PWRGD assertion)

1 = CPU2_ITP, 0 = SRC8

15

VSS_PCI

GND

Ground for outputs.

16

VDD_48

PWR

3.3V Power supply for outputs and PLL.

17

USB_48/FSA

I/O

3.3V tolerant input for CPU frequency selection/fixed 48 MHz clock output.

Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifica-

tions.

18

VSS_48

GND

Ground for outputs.

19

VDD_IO

PWR

0.7V Power supply for outputs.

20

SRC0/DOT96

O, DIF 100 MHz Differential serial reference clocks/Fixed 96 MHz clock output.

Selected via I2C default is SRC0.

21

SRC0#/DOT96#

O, DIF 100 MHz Differential serial reference clocks/Fixed 96 MHz clock output.

Selected via I2C default is SRC0.

22

VSS_IO

GND

Ground for PLL2.

23

VDD_PLL3

PWR

3.3V Power supply for PLL3

24

SRC1/LCD_100/27M_SS

O, DIF 100 MHz Differential serial reference clocks/100 MHz LCD video clock. Default

SRC1

GCLK_SEL

Pin13

Pin14

Pin24

Pin 25

0

DOT96T DOT96C SRC1T/LCD_100T SRC1C/LCD_100C

1

SRCT0

SRCC0

27M_NSS

27M_SS

相关PDF资料 |

PDF描述 |

|---|---|

| SL28506BZC-2T | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| SL28506BOC-2 | PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| SL28506BZIT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO64 |

| SL28548ALC-2T | PROC SPECIFIC CLOCK GENERATOR, QCC64 |

| SL28610BLC | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, QCC48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL28506BZC | 功能描述:时钟发生器及支持产品 CK505 v1.1 PCIe Gen2 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28506BZC-2 | 功能描述:时钟发生器及支持产品 CK505 v1.1 PCIe Gen2 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28506BZC-2T | 功能描述:时钟发生器及支持产品 CK505 v1.1 PCIe Gen2 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28506BZCT | 功能描述:时钟发生器及支持产品 CK505 v1.1 PCIe Gen2 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28506BZI | 功能描述:时钟发生器及支持产品 CK505 v1.1 PCIe Gen2 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。