- 您现在的位置:买卖IC网 > PDF目录98082 > SL28PCIE26ALC (SILICON LABORATORIES) OTHER CLOCK GENERATOR, QCC32 PDF资料下载

参数资料

| 型号: | SL28PCIE26ALC |

| 厂商: | SILICON LABORATORIES |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | OTHER CLOCK GENERATOR, QCC32 |

| 封装: | 5 X 5 MM, LEAD FREE, QFN-32 |

| 文件页数: | 2/14页 |

| 文件大小: | 232K |

| 代理商: | SL28PCIE26ALC |

SL28PCIe26

DOC#: SP-AP-0774 (Rev. AA)

Page 10 of 14

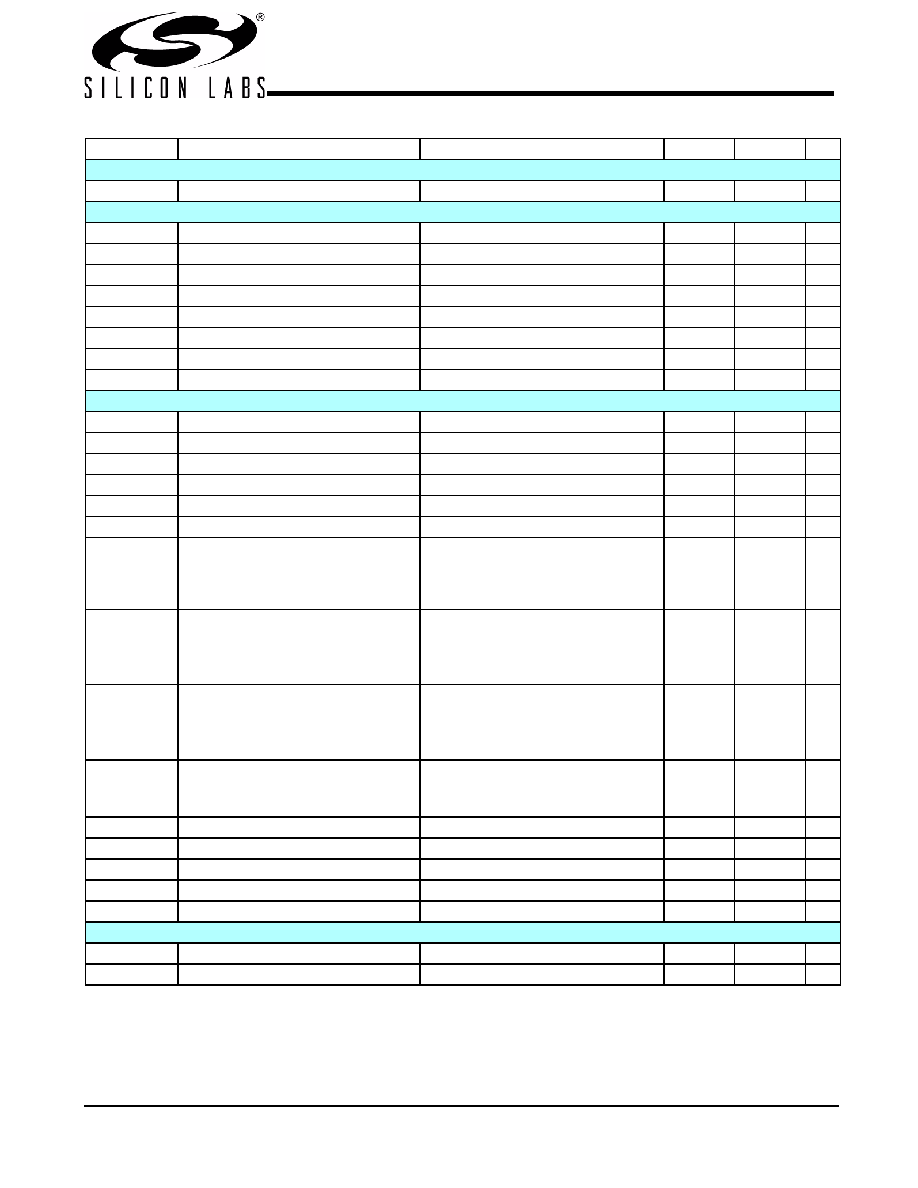

AC Electrical Specifications

Parameter

Description

Condition

Min.

Max.

Unit

Crystal

LACC

Long-term Accuracy

Measured at VDD/2 differential

–

250

ppm

Clock Input

TDC

CLKIN Duty Cycle

Measured at VDD/2

47

53

%

TR/TF

CLKIN Rise and Fall Times

Measured between 0.2VDD and 0.8VDD

0.5

4.0

V/ns

TCCJ

CLKIN Cycle to Cycle Jitter

Measured at VDD/2

–

250

ps

TLTJ

CLKIN Long Term Jitter

Measured at VDD/2

–

350

ps

VIH

Input High Voltage

XIN / CLKIN pin

2

VDD+0.3

V

VIL

Input Low Voltage

XIN / CLKIN pin

–

0.8

V

IIH

Input HighCurrent

XIN / CLKIN pin, VIN = VDD

–

35

uA

IIL

Input LowCurrent

XIN / CLKIN pin, 0 < VIN <0.8

-35

–

uA

SRC at 0.7V

TDC

Duty Cycle

Measured at 0V differential

45

55

%

TPERIOD

Period

Measured at 0V differential at 0.1s

9.99900

10.0010

ns

TPERIODSS

Period, SSC

Measured at 0V differential at 0.1s

10.02406

10.02607

ns

TPERIODAbs

Absolute Period

Measured at 0V differential at 1 clock

9.87400

10.1260

ns

TPERIODSSAbs Absolute Period, SSC

Measured at 0V differential at 1 clock

9.87406

10.1762

ns

TCCJ

Cycle to Cycle Jitter

Measured at 0V differential

–

125

ps

RMSGEN1

Output PCIe* Gen1 REFCLK phase

jitter

BER = 1E-12 (including PLL BW 8 - 16

MHz, ζ = 0.54, Td=10 ns,

Ftrk=1.5 MHz)

0108

ps

RMSGEN2

Output PCIe* Gen2 REFCLK phase

jitter

Includes PLL BW 8 - 16 MHz, Jitter

Peaking = 3dB, ζ = 0.54, Td=10 ns),

Low Band, F < 1.5MHz

03.0

ps

RMSGEN2

Output PCIe* Gen2 REFCLK phase

jitter

Includes PLL BW 8 - 16 MHz, Jitter

Peaking = 3dB, ζ = 0.54, Td=10 ns),

Low Band, F < 1.5MHz

03.1

ps

RMSGEN3

Output phase jitter impact – PCIe*

Gen3

Includes PLL BW 2 - 4 MHz,

CDR = 10MHz)

01.0

ps

LACC

Long Term Accuracy

Measured at 0V differential

–

100

ppm

TR / TF

Rising/Falling Slew Rate

Measured differentially from ±150 mV

2.5

8

V/ns

VHIGH

Voltage High

1.15

V

VLOW

Voltage Low

–0.3

–

V

VOX

Crossing Point Voltage at 0.7V Swing

300

550

mV

ENABLE/DISABLE and SET-UP

TSTABLE

Clock Stabilization from Power-up

–

1.8

ms

TSS

Stopclock Set-up Time

10.0

–

ns

相关PDF资料 |

PDF描述 |

|---|---|

| SL28SRC01BZC | OTHER CLOCK GENERATOR, PDSO16 |

| SL38160AZI-18AH | 148.5 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| SL38160AZC-24AH | 148.5 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| SL38160ZI-XXXT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO16 |

| SL5500_NL | 1 CHANNEL TRANSISTOR OUTPUT OPTOCOUPLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL28PCIe26ALCT | 功能描述:时钟发生器及支持产品 PCIE Clk Gen Xin 25M -->4 PCIE out Gen3 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28PCIe26ALI | 功能描述:时钟发生器及支持产品 PCIE Clk Gen Xin 25M -->4 PCIE out Gen3 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28PCIe26ALIT | 功能描述:时钟发生器及支持产品 PCIE Clk Gen Xin 25M -->4 PCIE out Gen3 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28PCIe30ALC | 功能描述:时钟发生器及支持产品 6outputs 3sngl ended 25MHz crystal input RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| SL28PCIe30ALCT | 功能描述:时钟发生器及支持产品 6outputs 3sngl ended 25MHz crystal input RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。