- 您现在的位置:买卖IC网 > PDF目录98083 > SM5L3 (SHARP ELECTRONICS CORP) 4-BIT, MROM, MICROCONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | SM5L3 |

| 厂商: | SHARP ELECTRONICS CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER, PQFP80 |

| 封装: | 14 X 20 MM, PLASTIC, QFP-80 |

| 文件页数: | 13/27页 |

| 文件大小: | 164K |

| 代理商: | SM5L3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页当前第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

SM5L1/SM5L2/SM5L3

4-Bit Single Chip Microcomputers

20

Microcomputer Data Sheet

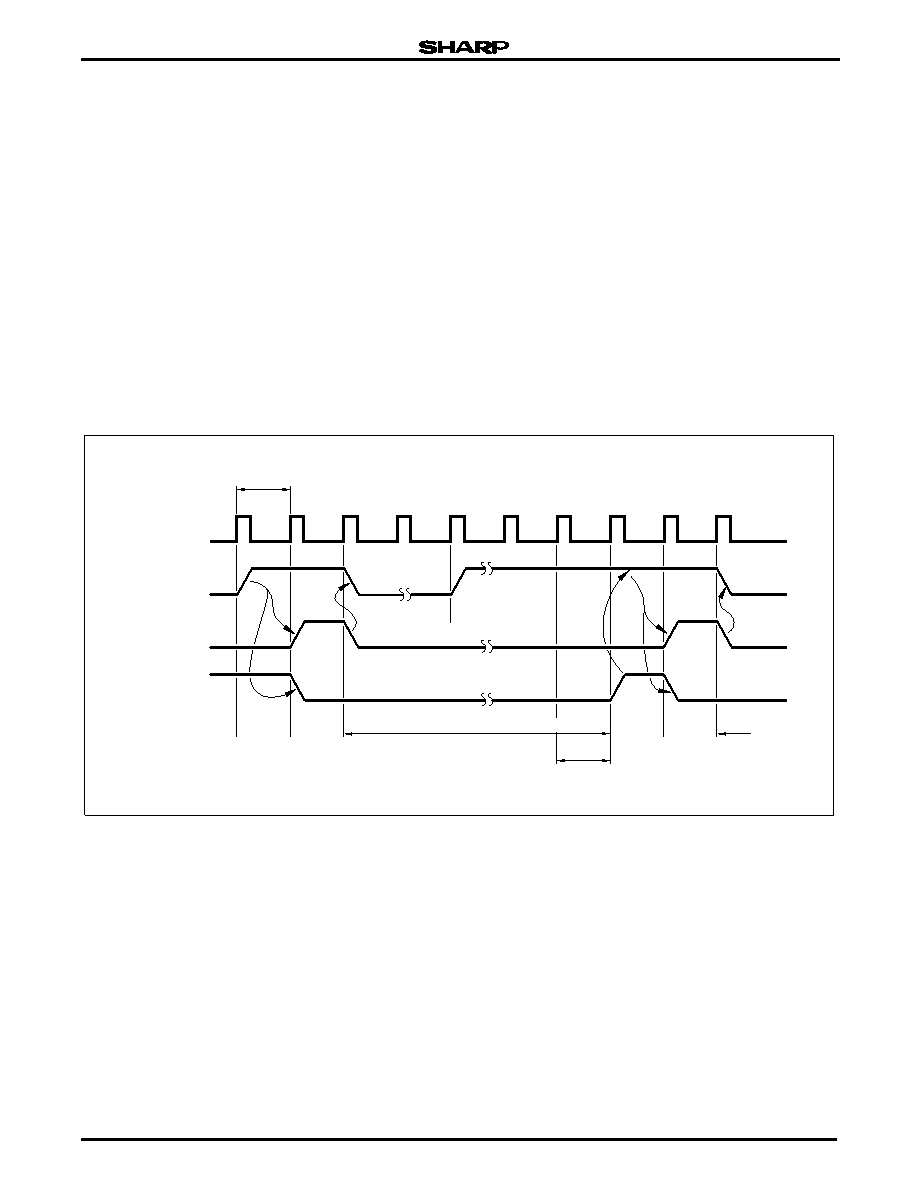

When the IME flag is set, the interrupt circuit acti-

vates according to the interrupt request and a subrou-

tine jump is performed to the specified address. The

jump destinations according to interrupt origin are

shown in Table 5. When the IME flag is cleared, an

interrupt is not accepted even if an interrupt request is

generated. The interrupt timing is shown in Figure 25

and Figure 26. The timing chart in Figure 25 shows the

interrupt enable state when an interrupt request has

been generated. In this case, the interrupt processing

signal INT goes HIGH, one instruction cycle after the

interrupt request flag is set. When INT goes HIGH, the

contents of the program counter are pushed into the

stack register and execution jumps to the specified

address. At this time, the INT signal and the IME flag

are cleared to establish the interrupt disable mode. The

IME flag is set again when the RTNI instruction is exe-

cuted to establish the interrupt enable mode.

The timing chart shown in Figure 26 shows the state

when interrupts are enabled while multiple interrupts

are generated. In this case, a subroutine jump is per-

formed according to the interrupt having the highest pri-

ority. When returning from the subroutine by executing

the RTNI instruction, the instruction (two words are

executed for a two-word instruction) at the location of

return is executed and the interrupt for the next highest

priority is accepted.

If an interrupt request is generated during execution

of a two cycle instruction, the instruction is executed

after which interrupt processing is performed. If con-

secutive LAX instructions are skipped or if the SKIP

conditions are satisfied, the skip operation is termi-

nated after which interrupt processing is performed.

NOTE: Figures 25 and 26 show non-masked interrupt request flags.

Figure 25. Interrupt Timing Chart

INSTRUCTION

CYCLE

INTERRUPT PROCESSING ROUTINE

INTERRUPT

PROCESSING

ROUTINE

RTNI

INSTRUCTION

SYSTEM CLOCK

INTERRUPT

REQUEST FLAG

INT SIGNAL

INTERRUPT

ENABLE FLAG

5L1-25

相关PDF资料 |

PDF描述 |

|---|---|

| SM802104UMG | 212.5 MHz, OTHER CLOCK GENERATOR, QCC24 |

| SM802105UMG | 312.5 MHz, OTHER CLOCK GENERATOR, QCC24 |

| SM802108UMG | 156.25 MHz, OTHER CLOCK GENERATOR, QCC24 |

| SMC34C90 | PCI BUS CONTROLLER, PBGA256 |

| SMC6247 | 4-BIT, MROM, 1 MHz, MICROCONTROLLER, PQFP160 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SM5LS | 制造商:Potter & Brumfield 功能描述:RELAY SPDT .25A 5000 ohm special |

| SM5LS-5000 | 制造商:P&B 功能描述: 制造商:TE Connectivity 功能描述: |

| SM5M2 | 制造商:SHARP 制造商全称:Sharp Electrionic Components 功能描述:4-Bit Single-Chip Microcomputer(LCD Driver) |

| SM-5R1000FE6 | 功能描述:RES 0.1 OHM 1% 4W 制造商:vishay dale 系列:SM 包装:剪切带(CT) 零件状态:Digi-Key 停止供應 电阻值:100 mOhms 容差:±1% 功率(W):4W 成分:绕线 特性:- 温度系数:- 工作温度:-55°C ~ 275°C 封装/外壳:8230 J 形引线 供应商器件封装:SM-5 大小/尺寸:0.820" 长 x 0.295" 宽(20.83mm x 7.49mm) 高度 - 安装(最大值):0.305"(7.75mm) 端子数:2 故障率:- 标准包装:1 |

| SM-5R5000FE6 | 功能描述:RES 0.5 OHM 1% 4W 制造商:vishay dale 系列:SM 包装:剪切带(CT) 零件状态:Digi-Key 停止供應 电阻值:500 mOhms 容差:±1% 功率(W):4W 成分:绕线 特性:- 温度系数:- 工作温度:-55°C ~ 275°C 封装/外壳:8230 J 形引线 供应商器件封装:SM-5 大小/尺寸:0.820" 长 x 0.295" 宽(20.83mm x 7.49mm) 高度 - 安装(最大值):0.305"(7.75mm) 端子数:2 故障率:- 标准包装:1 |

发布紧急采购,3分钟左右您将得到回复。