- 您现在的位置:买卖IC网 > PDF目录97087 > SN74LVTH16652MEAX (FAIRCHILD SEMICONDUCTOR CORP) LVT SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 PDF资料下载

参数资料

| 型号: | SN74LVTH16652MEAX |

| 厂商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分类: | 总线收发器 |

| 英文描述: | LVT SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| 封装: | 0.300 INCH, MO-118, SSOP-56 |

| 文件页数: | 7/9页 |

| 文件大小: | 87K |

| 代理商: | SN74LVTH16652MEAX |

7

www.fairchildsemi.com

7

4

L

V

TH16

652

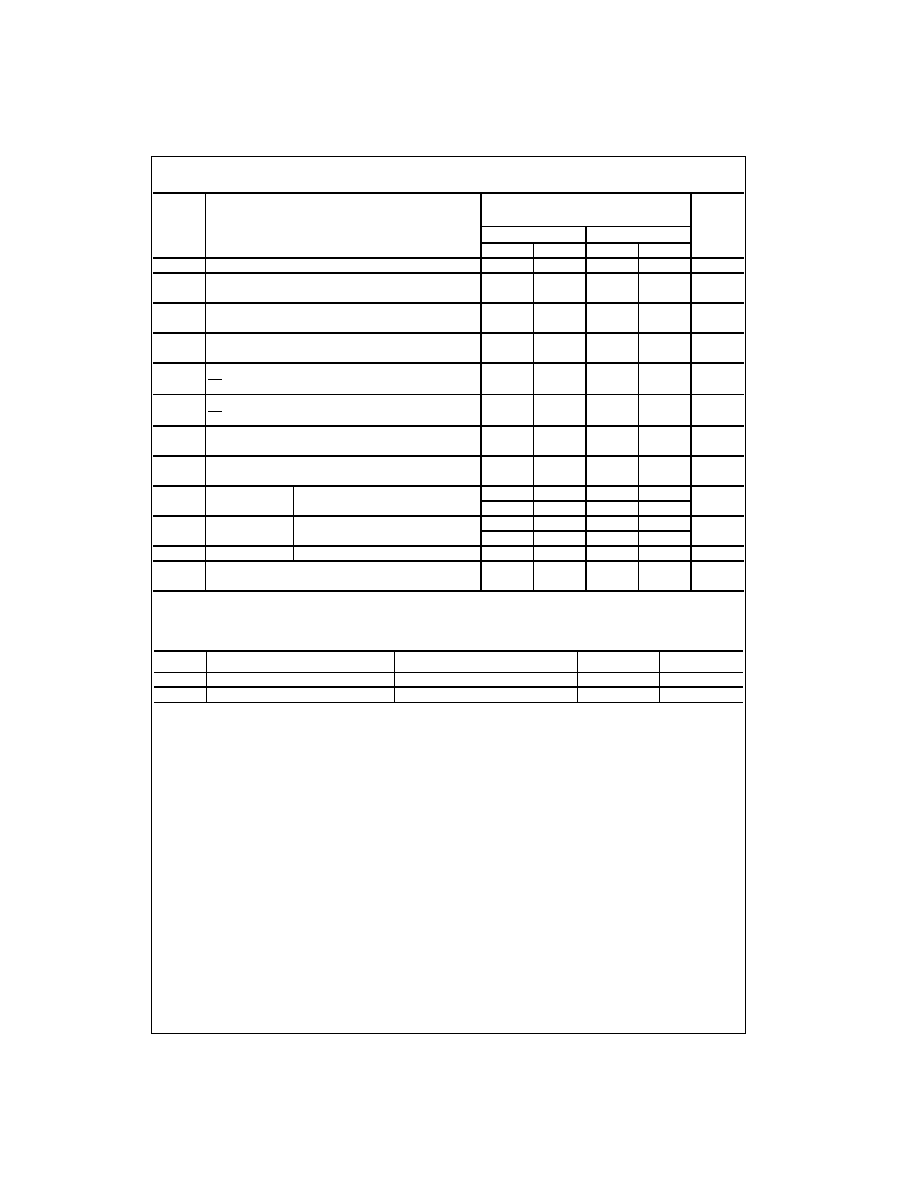

AC Electrical Characteristics

Note 9: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The

specification applies to any outputs switching in the same direction, either HIGH-to-LOW (tOSHL) or LOW-to-HIGH (tOSLH).

Capacitance (Note 10)

Note 10: Capacitance is measured at frequency f

= 1 MHz, per MIL-STD-883, Method 3012.

Symbol

Parameter

TA = 40°C to +85°C

Units

CL = 50 pF, RL = 500

VCC = 3.3V ± 0.3V

VCC = 2.7V

Min

Max

Min

Max

fMAX

Maximum Clock Frequency

150

MHz

tPHL

Propagation Delay

1.3

4.8

1.3

5.4

ns

tPLH

CPAB or CPBA to A or B

1.3

5.1

1.3

5.6

tPHL

Propagation Delay

1.0

4.5

1.0

5.1

ns

tPLH

Data to A or B

1.0

4.4

1.0

4.7

tPHL

Propagation Delay

1.0

4.9

1.0

5.5

ns

tPLH

SBA or SAB to A or B

1.0

4.8

1.0

5.4

tPZL

Output Enable Time

1.0

4.9

1.0

5.8

ns

tPZH

OE to A

1.04.8

1.05.8

tPLZ

Output Disable Time

1.6

5.6

1.6

6.1

ns

tPHZ

OE to A

2.05.4

2.06.1

tPZL

Output Enable Time

1.3

5.0

1.3

5.4

ns

tPZH

OE to B

1.3

4.8

1.3

5.4

tPLZ

Output Disable Time

1.3

5.5

1.3

6.2

ns

tPHZ

OE to B

1.3

5.6

1.3

6.3

tS

Setup Time

A or B before CPAB or CPBA, Data HIGH

1.2

1.5

ns

A or B before CPAB or CPBA, Data LOW

2.0

2.8

tH

Hold Time

A or B before CPAB or CPBA, Data HIGH

0.5

0.0

ns

A or B before CPAB or CPBA, Data LOW

0.5

tW

Pulse Width

CPAB or CPBA HIGH or LOW

3.3

ns

tOSHL

Output to Output Skew (Note 9)

1.0

ns

tOSLH

1.0

Symbol

Parameter

Conditions

Typical

Units

CIN

Input Capacitance

VCC = Open, VI = 0V or VCC

4pF

CI/O

Input/Output Capacitance

VCC = 3.0V, VO = 0V or VCC

8pF

相关PDF资料 |

PDF描述 |

|---|---|

| SN74LVTH16652MEA | LVT SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PDSO56 |

| SN74LVTH16835DGG | LVT SERIES, 18-BIT DRIVER, TRUE OUTPUT, PDSO56 |

| SN74LVTH240ADW | LVT SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

| SN74LVTH240ADBR | LVT SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

| SN74LVTH573DGVR | LVT SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74LVTH16835DGGR | 功能描述:通用总线函数 Tri-State ABT 18-Bit RoHS:否 制造商:Texas Instruments 逻辑类型:CMOS 逻辑系列:74VMEH 电路数量:1 开启电阻(最大值): 传播延迟时间:10.1 ns 电源电压-最大:3.45 V 电源电压-最小:3.15 V 最大工作温度:+ 85 C 最小工作温度:0 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16835DL | 功能描述:总线收发器 Tri-State ABT 18-Bit RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16835DLG4 | 功能描述:总线收发器 8-Bit To 9-Bit Parity Transceivers RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16835DLR | 功能描述:总线收发器 3.3V ABT 18-Bit Univ Bus Drvr W/3-St Otpt RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16952DGGR | 功能描述:总线收发器 16bit ABT RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

发布紧急采购,3分钟左右您将得到回复。