- 您现在的位置:买卖IC网 > PDF目录373461 > SN74LVTH16952DGG (Texas Instruments, Inc.) Ceramic Chip Capacitors / MIL-PRF-55681; Capacitance [nom]: 0.018uF; Working Voltage (Vdc)[max]: 50V; Capacitance Tolerance: +/-10%; Dielectric: Multilayer Ceramic; Temperature Coefficient: X7R (BX); Lead Style: Surface Mount Chip; Lead Dimensions: 1206; Termination: 100% Tin (Sn); Body Dimensions: 0.125" x 0.062" x 0.051"; Container: Bag; Features: MIL-PRF-55681: S Failure Rate PDF资料下载

参数资料

| 型号: | SN74LVTH16952DGG |

| 厂商: | Texas Instruments, Inc. |

| 元件分类: | 通用总线功能 |

| 英文描述: | Ceramic Chip Capacitors / MIL-PRF-55681; Capacitance [nom]: 0.018uF; Working Voltage (Vdc)[max]: 50V; Capacitance Tolerance: +/-10%; Dielectric: Multilayer Ceramic; Temperature Coefficient: X7R (BX); Lead Style: Surface Mount Chip; Lead Dimensions: 1206; Termination: 100% Tin (Sn); Body Dimensions: 0.125" x 0.062" x 0.051"; Container: Bag; Features: MIL-PRF-55681: S Failure Rate |

| 中文描述: | 的3.3V ABT生根粉16位收发登记,3态输出 |

| 文件页数: | 1/13页 |

| 文件大小: | 211K |

| 代理商: | SN74LVTH16952DGG |

SN54LVTH16952, SN74LVTH16952

3.3-V ABT 16-BIT REGISTERED TRANSCEIVERS

WITH 3-STATE OUTPUTS

SCBS697G – JULY 1997 – REVISED APRIL 2000

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Members of the Texas Instruments

Widebus

Family

State-of-the-Art Advanced BiCMOS

Technology (ABT) Design for 3.3-V

Operation and Low Static-Power

Dissipation

Support Mixed-Mode Signal Operation (5-V

Input and Output Voltages With 3.3-V V

CC

)

Support Unregulated Battery Operation

Down to 2.7 V

Typical V

OLP

(Output Ground Bounce)

<0.8 V at V

CC

= 3.3 V, T

A

= 25

°

C

I

off

and Power-Up 3-State Support Hot

Insertion

Bus Hold on Data Inputs Eliminates the

Need for External Pullup/Pulldown

Resistors

Distributed V

CC

and GND Pins Minimize

High-Speed Switching Noise

Flow-Through Architecture Optimizes PCB

Layout

Latch-Up Performance Exceeds 500 mA Per

JESD 17

ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

Package Options Include Plastic Shrink

Small-Outline (DL) and Thin Shrink

Small-Outline (DGG) Packages and 380-mil

Fine-Pitch Ceramic Flat (WD) Package

description

The ’LVTH16952 devices are 16-bit registered transceivers designed for low-voltage (3.3-V) V

CC

operation, but

with the capability to provide a TTL interface to a 5-V system environment.

These devices can be used as two 8-bit transceivers or one 16-bit transceiver. Data on the A or B bus is stored

in the registers on the low-to-high transition of the clock (CLKAB or CLKBA) input, provided that the clock-enable

(CLKENAB or CLKENBA) input is low. Taking the output-enable (OEAB or OEBA) input low accesses the data

on either port.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

When V

CC

is between 0 and 1.5 V, the devices are in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 1.5 V, OE should be tied to V

CC

through a pullup resistor;

the minimum value of the resistor is determined by the current-sinking capability of the driver.

Copyright

2000, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested

unless otherwise noted. On all other products, production

processing does not necessarily include testing of all parameters.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Widebus is a trademark of Texas Instruments.

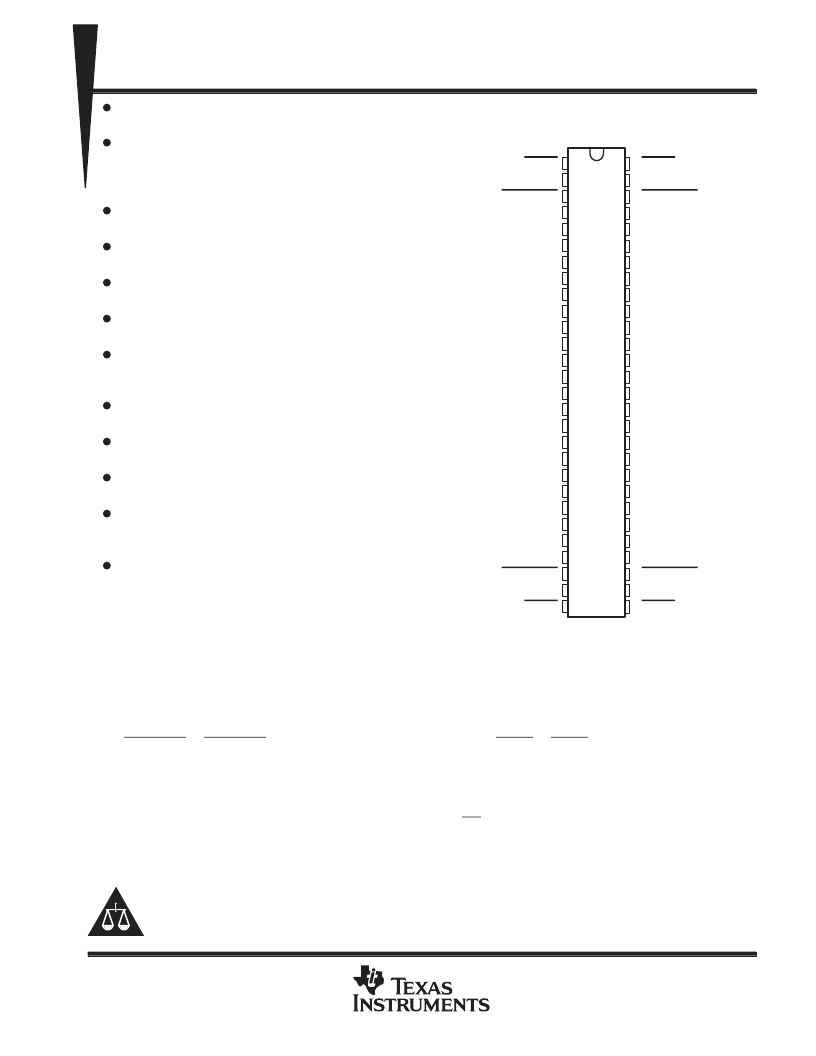

SN54LVTH16952 . . . WD PACKAGE

SN74LVTH16952 . . . DGG OR DL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

1OEAB

1CLKAB

1CLKENAB

GND

1A1

1A2

V

CC

1A3

1A4

1A5

GND

1A6

1A7

1A8

2A1

2A2

2A3

GND

2A4

2A5

2A6

V

CC

2A7

2A8

GND

2CLKENAB

2CLKAB

2OEAB

1OEBA

1CLKBA

1CLKENBA

GND

1B1

1B2

V

CC

1B3

1B4

1B5

GND

1B6

1B7

1B8

2B1

2B2

2B3

GND

2B4

2B5

2B6

V

CC

2B7

2B8

GND

2CLKENBA

2CLKBA

2OEBA

相关PDF资料 |

PDF描述 |

|---|---|

| SN54LVTH182245 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3V ABT 扫描检测装置带18位总线收发器) |

| SN54LVTH18245 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3V ABT 扫描检测装置带18位总线收发器) |

| SN74LVTH182245 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3V ABT 扫描检测装置带18位总线收发器) |

| SN74LVTH18245 | 3.3-V ABT Scan Test Device With 18-Bit Universal Bus Transceivers(3.3V ABT 扫描检测装置带18位总线收发器) |

| SN54LVTH182504AHV | Octal 3-State Inverting Buffer/Line Driver/Line Receiver; Package: SOEIAJ-20; No of Pins: 20; Container: Rail; Qty per Container: 40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74LVTH16952DGGR | 功能描述:总线收发器 16bit ABT RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16952DL | 功能描述:总线收发器 16bit ABT RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16952DLG4 | 功能描述:总线收发器 10-Bit Buffer/Driver With 3-State Outputs RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH16952DLR | 功能描述:总线收发器 3.3 V ABT 16-Bit Reg Trncvr W/3-St Otpt RoHS:否 制造商:Fairchild Semiconductor 逻辑类型:CMOS 逻辑系列:74VCX 每芯片的通道数量:16 输入电平:CMOS 输出电平:CMOS 输出类型:3-State 高电平输出电流:- 24 mA 低电平输出电流:24 mA 传播延迟时间:6.2 ns 电源电压-最大:2.7 V, 3.6 V 电源电压-最小:1.65 V, 2.3 V 最大工作温度:+ 85 C 封装 / 箱体:TSSOP-48 封装:Reel |

| SN74LVTH182502APM | 功能描述:特定功能逻辑 10-Bit Buffer/Driver With 3-State Outputs RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。