- 您现在的位置:买卖IC网 > PDF目录98027 > SPC5121YVY400BR (FREESCALE SEMICONDUCTOR INC) RISC PROCESSOR, PBGA516 PDF资料下载

参数资料

| 型号: | SPC5121YVY400BR |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | RISC PROCESSOR, PBGA516 |

| 封装: | 27 X 27 MM, 2.25 MM HEIGHT, 1 MM PITCH, ROHS COMPLIANT, PLASTIC, TFBGA-516 |

| 文件页数: | 40/86页 |

| 文件大小: | 719K |

| 代理商: | SPC5121YVY400BR |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页当前第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

Electrical and Thermal Characteristics

MPC5121E/MPC5123 Data Sheet, Rev. 3

Freescale Semiconductor

45

Faster ATA modes (i.e., UDMA 0, 1, 2) are supported when the system is running at a sufficient frequency to provide adequate

data transfer rates. Adequate data transfer rates are a function of the following:

The MPC5121e/MPC5123 operating frequency (IP bus clock frequency)

Internal MPC5121e/MPC5123 bus latencies

Other system load dependent variables

The ATA clock is the same frequency as the IP bus clock in MPC5121e/MPC5123. See the MPC5121e/MPC5123 Reference

Manual.

NOTE

All output timing numbers are specified for nominal 50 pF loads.

3.3.9.1

PATA Timing Parameters

In the timing equations, some timing parameters are used. These parameters depend on the implementation of the ATA interface

in silicon, the bus transceiver used, the cable delay and cable skew. The parameters shown in Table 3-25 specify the ATA timing.

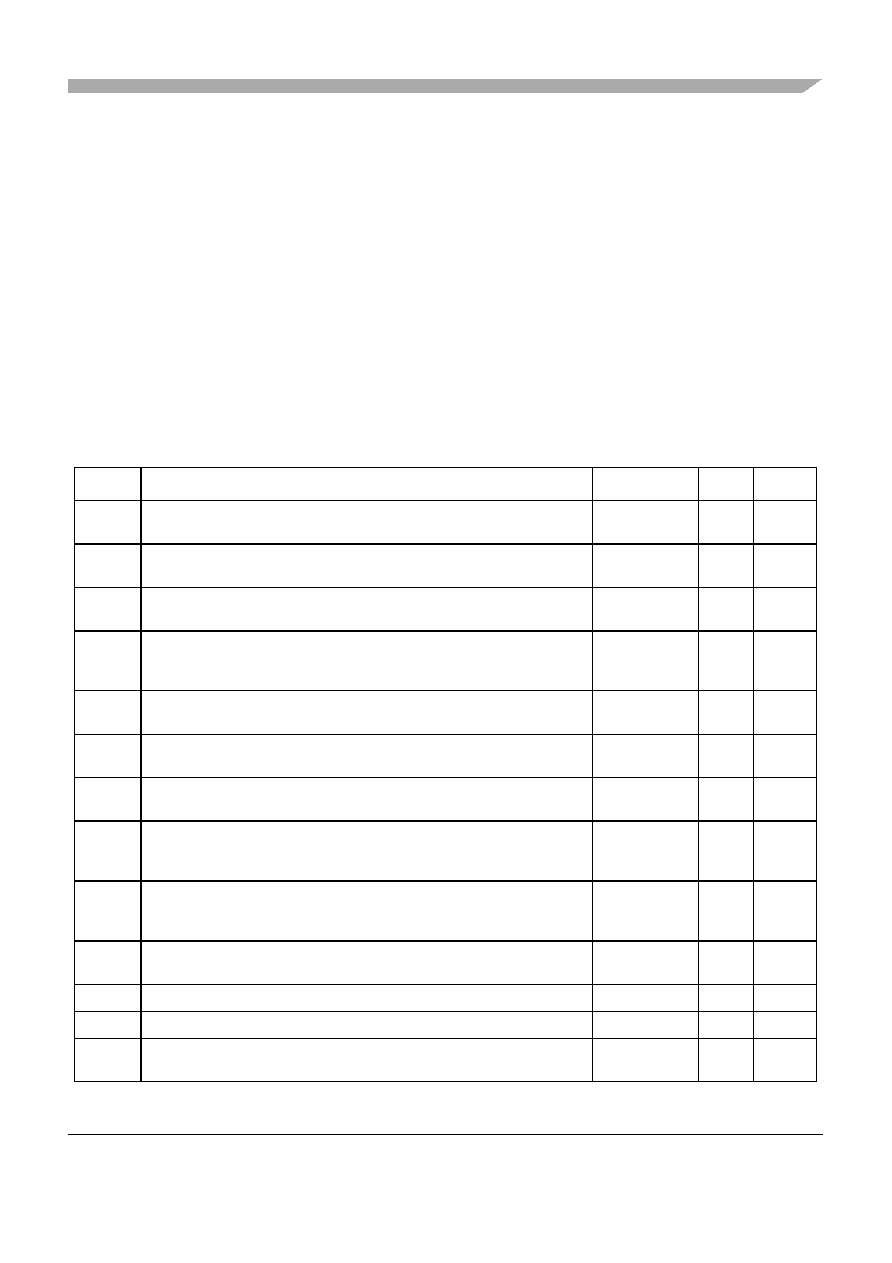

Table 3-25. PATA Timing Parameters

Name

Meaning

Controlled by

Value

SpecID

T

PATA Bus clock period

MPC5121E/M

PC5123

15 ns

A9.1

ti_ds

Set-up time ATA_DATA to ATA_IORDY edge (UDMA-in only)

MPC5121E/M

PC5123

2 ns

A9.2

ti_dh

Hold time ATA_IORDY edge to ATA_DATA (UDMA-in only)

MPC5121E/M

PC5123

5 ns

A9.3

tco

Propagation delay bus clock L-to-H to: ATA_CS0, ATA_CS1, ATA_DA2,

ATA_DA1, ATA_DA0, ATA_DIOR, ATA_DIOW, ATA_DMACK, ATA_DATA,

ATA_BUFFER_EN

MPC5121E/M

PC5123

2 ns

A9.4

tsu

Set-up time ATA_DATA to bus clock L-to-H

MPC5121E/M

PC5123

2 ns

A9.5

tsui

Set-up time ATA_IORDY to bus clock H-to-L

MPC5121E/M

PC5123

2 ns

A9.6

thi

Hold time ATA_IORDY to bus clock H to L

MPC5121E/M

PC5123

2 ns

A9.7

tskew1

Max difference in propagation delay bus clock L-to-H to any of following

signals: ATA_CS0, ATA_CS1, ATA_DA2, ATA_DA1, ATA_DA0, ATA_DIOR,

ATA_DIOW, ATA_DMACK, ATA_DATA (WRITE), ATA_BUFFER_EN

MPC5121E/M

PC5123

1.7 ns

A9.8

tskew2

Max difference in buffer propagation delay for any of following signals:

ATA_CS0, ATA_CS1, ATA_DA2, ATA_DA1, ATA_DA0, ATA_DIOR,

ATA_DIOW, ATA_DMACK, ATA_DATA (WRITE), ATA_BUFFER_EN

Transceiver

A9.9

tskew3

Max difference in buffer propagation delay for any of following signals:

ATA_IORDY, ATA_DATA (read)

Transceiver

A9.10

tbuf

Max buffer propagation delay

Transceiver

A9.11

tcable1

Cable propagation delay for ata_data

Cable

A9.12

tcable2

Cable propagation delay for control signals: ATA_DIOR, ATA_DIOW,

ATA_IORDY, ATA_DMACK

Cable

A9.13

相关PDF资料 |

PDF描述 |

|---|---|

| MPC601CQ50A | RISC PROCESSOR |

| MPC601CQ66A | 32-BIT, 66 MHz, RISC PROCESSOR, CQFP304 |

| MPC604ERX300XX | RISC PROCESSOR, CBGA255 |

| MPC7410RX550PE | 32-BIT, 550 MHz, RISC PROCESSOR, CBGA360 |

| MPC7410RX450PER2 | 32-BIT, 450 MHz, RISC PROCESSOR, CBGA360 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SPC5123YVY300B | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Advance Information |

| SPC5123YVY300BR | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Advance Information |

| SPC5123YVY400B | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:e300 Power Architecture processor core |

| SPC5123YVY400BR | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:e300 Power Architecture processor core |

| SPC5125 | 制造商:ELECTROMAGNETIC CORPORATI 功能描述:_ |

发布紧急采购,3分钟左右您将得到回复。