- 您现在的位置:买卖IC网 > PDF目录10951 > SSM2604CPZ-REEL7 (Analog Devices Inc)IC AUDIO CODEC LP 20-LFCSP PDF资料下载

参数资料

| 型号: | SSM2604CPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 5/28页 |

| 文件大小: | 0K |

| 描述: | IC AUDIO CODEC LP 20-LFCSP |

| 标准包装: | 1 |

| 类型: | 立体声音频 |

| 数据接口: | 串行 |

| 分辨率(位): | 24 b |

| ADC / DAC 数量: | 2 / 2 |

| 三角积分调变: | 无 |

| S/N 比,标准 ADC / DAC (db): | 90 / 100 |

| 电压 - 电源,模拟: | 1.8 V ~ 3.6 V |

| 电压 - 电源,数字: | 1.5 V ~ 3.6 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 20-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 20-LFCSP-VQ |

| 包装: | 标准包装 |

| 其它名称: | SSM2604CPZ-REEL7DKR |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页

Data Sheet

SSM2604

Rev. A | Page 13 of 28

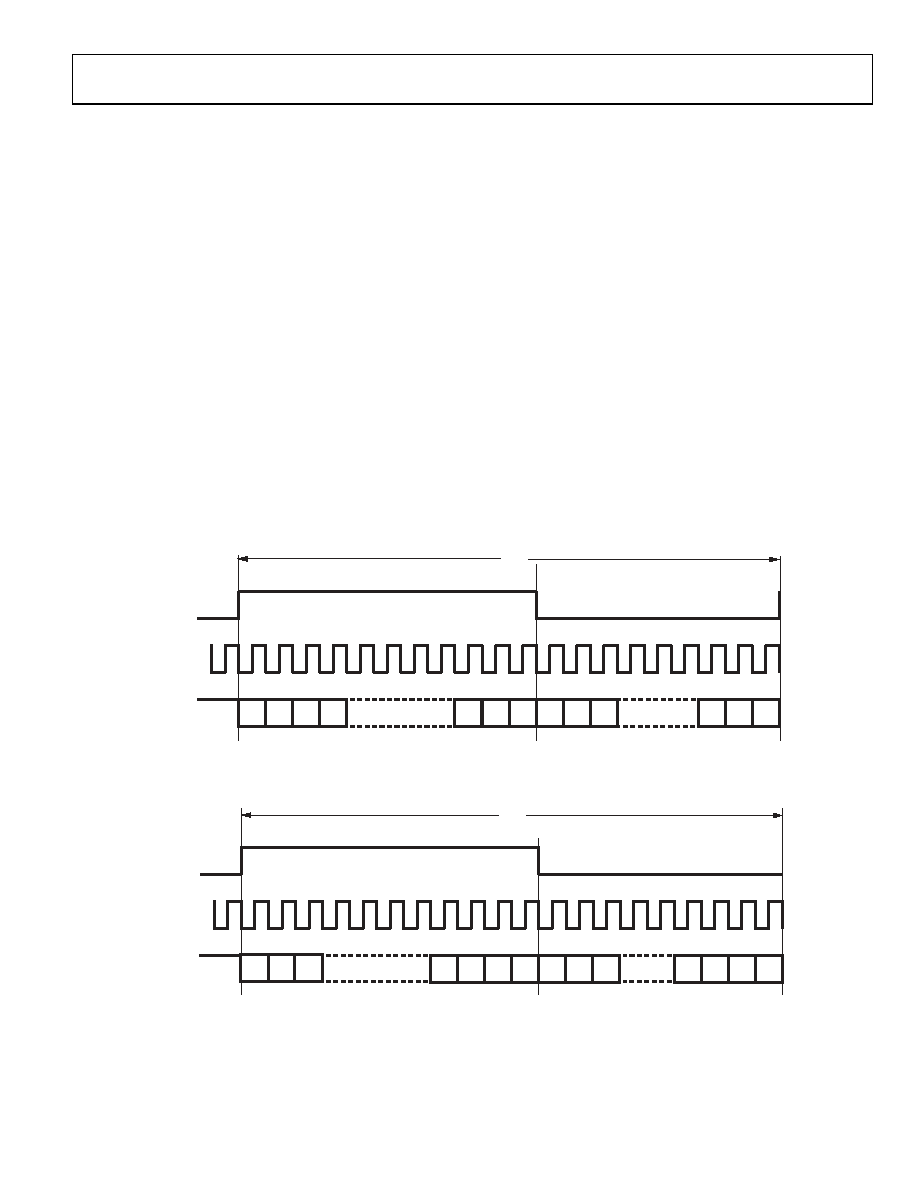

audio frame clock signal that separates left- and right-channel

data on the PBDAT lines.

The BCLK signal acts as the digital audio clock. Depending on

if the SSM2604 is in master or slave mode, the BCLK signal is

either an input or an output signal. During a playback opera-

tion, PBDAT and PBLRC must be synchronous to the BCLK

signal to avoid data corruption.

Digital Audio Data Sampling Rate

To accommodate a wide variety of commonly used DAC and

ADC sampling rates, the SSM2604 allows for two modes of

operation, normal and USB, selected by the USB bit (Register R8,

Bit D0).

In normal mode, the SSM2604 supports digital audio sampling

rates from 8 kHz to 96 kHz. Normal mode supports 256 fS and

384 fS based clocks. To select the desired sampling rate, the user

must set the appropriate sampling rate register in the SR control

bits (Register R8, Bit D2 to Bit D5) and match this selection to

the core clock frequency that is pulsed on the MCLK pin. See

Table 25 and Table 26 for guidelines.

In USB mode, the SSM2604 supports digital audio sampling

rates from 8 kHz to 96 kHz. USB mode is enabled on the

SSM2604 to support the common universal serial bus (USB)

clock rate of 12 MHz, or to support 24 MHz if the CLKDIV2

control register bit is activated. The user must set the appropriate

sampling rate in the SR control bits (Register R8, Bit D2 to Bit D5).

See Table 25 and Table 26 for guidelines.

Note that the sampling rate is generated as a fixed divider from

the MCLK signal. Because all audio processing references the

core MCLK signal, corruption of this signal, in turn, corrupts

the outgoing audio quality of the SSM2604. The BCLK/RECLRC/

RECDAT or BCLK/PBLRC/PBDAT signals must be synchronized

with MCLK in the digital audio interface circuit. MCLK must

be faster or equal to the BCLK frequency to guarantee that no

data is lost during data synchronization.

The BCLK frequency should be greater than

Sampling Rate × Word Length × 2

Ensuring that the BCLK frequency is greater than this value

guarantees that all valid data bits are captured by the digital

audio interface circuitry. For example, if a 32 kHz digital

audio sampling rate with a 32-bit word length is desired,

BCLK ≥ 2.048 MHz.

RECLRC/

PBLRC

BCLK

RECDAT/

PBDAT

12

3

4

N

X

N

1

2

LEFT CHANNEL

3

RIGHT CHANNEL

1/

fS

X = DON’T CARE.

0

69

78-

0

13

Figure 19. Left-Justified Audio Input Mode

RECLRC/

PBLRC

BCLK

RECDAT/

PBDAT

LEFT CHANNEL

RIGHT CHANNEL

1/

fS

X = DON’T CARE.

XN

X

3

21X

X

N

4

43

21

06

97

8-

01

4

Figure 20. Right-Justified Audio Input Mode

相关PDF资料 |

PDF描述 |

|---|---|

| MCIMX357DVM5B | PROCESSOR MULTIMEDIA 400PBGA |

| VI-26W-IY-F3 | CONVERTER MOD DC/DC 5.5V 50W |

| VI-26V-IY-F4 | CONVERTER MOD DC/DC 5.8V 50W |

| MAX9867ETJ+ | IC STEREO AUD CODEC LP 32TQFN-EP |

| MCIMX357DVM5BR2 | IC MPU I.MX35 400MAPBGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SSM2604-EVALZ | 功能描述:BOARD EVAL SSM2604 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:- 主要目的:电信,线路接口单元(LIU) 嵌入式:- 已用 IC / 零件:IDT82V2081 主要属性:T1/J1/E1 LIU 次要属性:- 已供物品:板,电源,线缆,CD 其它名称:82EBV2081 |

| SSM2605GY | 制造商:SSC 制造商全称:Silicon Standard Corp. 功能描述:P-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| SSM26PT | 制造商:CHENMKO 制造商全称:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

| SSM2761P-A | 制造商:SSC 制造商全称:Silicon Standard Corp. 功能描述:N-CHANNEL ENHANCEMENT MODE POWER MOSFET |

| SSM27APT | 制造商:CHENMKO 制造商全称:Chenmko Enterprise Co. Ltd. 功能描述:SCHOTTKY BARRIER RECTIFIER |

发布紧急采购,3分钟左右您将得到回复。