- 您现在的位置:买卖IC网 > PDF目录2110 > SSTUAF32866CHLF (IDT, Integrated Device Technology Inc)IC REGIST BUFF 25BIT DDR2 96-BGA PDF资料下载

参数资料

| 型号: | SSTUAF32866CHLF |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 19/30页 |

| 文件大小: | 0K |

| 描述: | IC REGIST BUFF 25BIT DDR2 96-BGA |

| 标准包装: | 270 |

| 逻辑类型: | 1:2 可配置寄存缓冲器 |

| 电源电压: | 1.7 V ~ 1.9 V |

| 位数: | 25,14 |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 96-LFBGA |

| 供应商设备封装: | 96-CABGA(13.5x5.5) |

| 包装: | 托盘 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

ICSSSTUAF32866C

25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

COMMERCIAL TEMPERATURE GRADE

25-BIT CONFIGURABLE REGISTERED BUFFER FOR DDR2

26

ICSSSTUAF32866C

7100/12

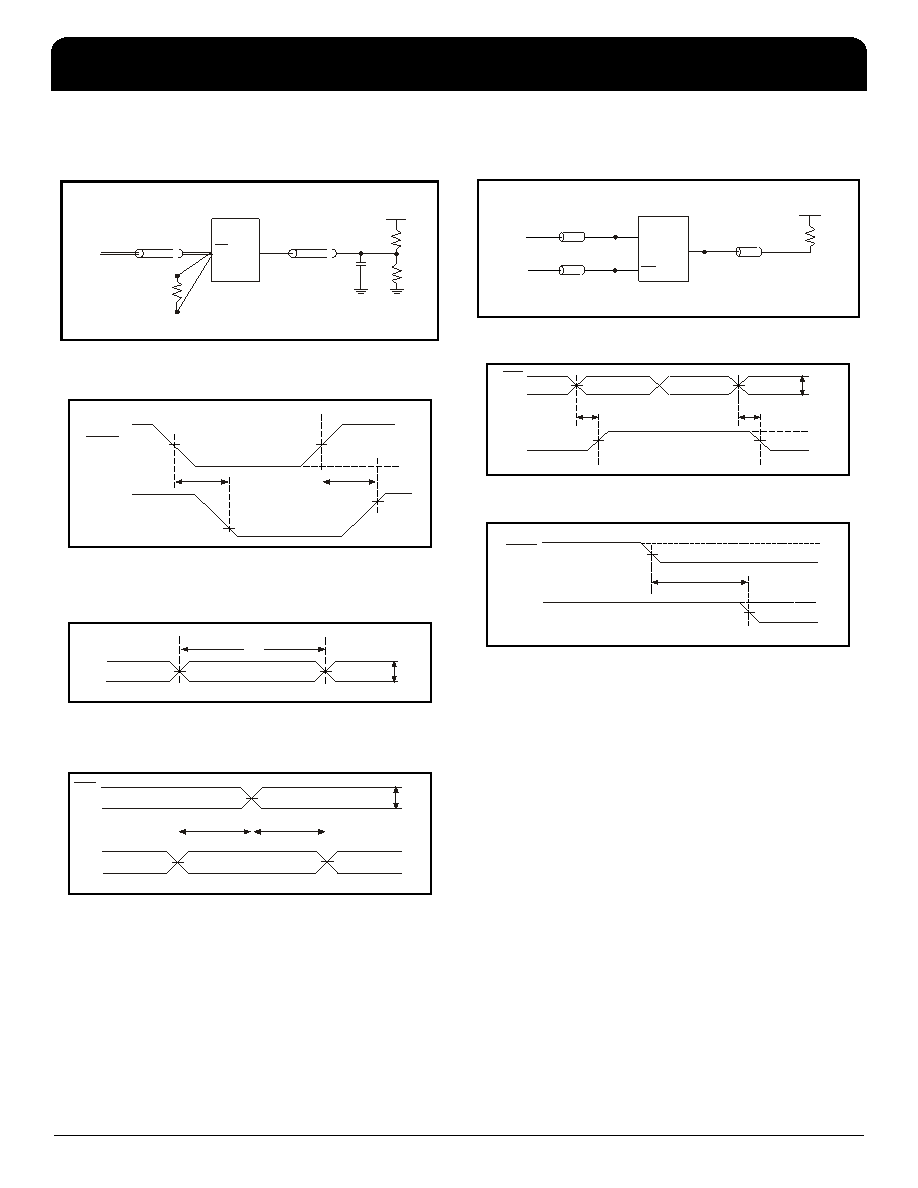

Test Circuits and Waveforms (VDD = 1.8V ± 0.1V)

Simulation Load Circuit

Voltage and Current Waveforms Inputs Active and Inactive

Times

Voltage Waveforms - Pulse Duration

Voltage Waveforms - Setup and Hold Times

Production-Test Load Circuit

Voltage Waveforms - Propagation Delay Times

NOTES:

1. CL includes probe and jig capacitance.

2. IDD tested with clock and data inputs held at VDD or GND, and

Io = 0mA

3. All input pulses are supplied by generators having the following

characteristics: PRR

≤10MHz, Zo = 50, input slew rate = 1 V/ns

±20% (unless otherwise specified).

4. The outputs are measured one at a time with one transition per

measurement.

5. VTT = VREF = VDD/2

6. VIH = VREF + 250mV (AC voltage levels) for differential inputs.

VIH = VDD for LVCMOS input.

7. VIL = VREF - 250mV (AC voltage levels) for differential inputs.

VIL = GND for LVCMOS input.

8. VID = 600mV.

9. tPLH and tPHL are the same as tPDM.

CL =30 pF

RL =1K

DUT

Out

RL= 100

CLK Inputs

TL =50

TL =350ps, 50

Test Point

CLK

VDD

RL =1K

Test Point

VDD

0V

VDD/2

LVCMOS

RESET

Input

IDD

VDD/2

tINACT

tACT

10%

90%

VICR

VID

VICR

Input

tW

VREF

VIH

VIL

VREF

Input

VICR

VID

tSU

tH

CLK

ZO =50

Test

Point

RL =50

DUT

Out

CLK Inputs

CLK

VDD/2

CLK

ZO =50

Test

Point

Test

Point

CLK

VICR

VID

tPLH

tPHL

Output

VOH

VOL

VICR

VTT

CLK

VOH

VOL

VIH

VIL

tRPHL

VDD/2

VTT

LVCMOS

RESET

Input

Output

相关PDF资料 |

PDF描述 |

|---|---|

| SSTUAF32868AHLF | IC REGIST BUFF 25BIT DDR2 176BGA |

| SSTUAF32868BHLFT | IC REG BUFFER 28BIT DDR2 176BGA |

| SSTUAF32869AHLFT | IC REGIST BUFF 25BIT DDR2 150BGA |

| SSTUB32864AHLF | IC REGIST BUFF 25BIT DDR2 96-BGA |

| SSTUB32866BHLFT | IC REGIST BUFF 25BIT DDR2 96-BGA |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SSTUAF32866CHLFT | 功能描述:IC REGIST BUFF 25BIT DDR2 96-BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| SSTUAF32868AHLF | 功能描述:寄存器 RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| SSTUAF32868AHLFT | 功能描述:寄存器 RoHS:否 制造商:NXP Semiconductors 逻辑类型:CMOS 逻辑系列:HC 电路数量:1 最大时钟频率:36 MHz 传播延迟时间: 高电平输出电流:- 7.8 mA 低电平输出电流:7.8 mA 电源电压-最大:6 V 最大工作温度:+ 125 C 封装 / 箱体:SOT-38 封装:Tube |

| SSTUAF32868BHLF | 功能描述:IC REG BUFFER 28BIT DDR2 176BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| SSTUAF32868BHLFT | 功能描述:IC REG BUFFER 28BIT DDR2 176BGA RoHS:是 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:- 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。