- 您现在的位置:买卖IC网 > PDF目录98143 > ST52F513G3B6 (STMICROELECTRONICS) 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 PDF资料下载

参数资料

| 型号: | ST52F513G3B6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP28 |

| 封装: | PLASTIC, DIP-28 |

| 文件页数: | 86/106页 |

| 文件大小: | 1340K |

| 代理商: | ST52F513G3B6 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页当前第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

13 SERIAL COMMUNICATION INTERFACE

The

Serial

Communication

Interface

(SCI)

integrated into ST52F510/F513/F514 provides a

general purpose shift register peripheral, several

widely distributed devices to be linked, through

their SCI subsystem. SCI gives a serial interface

providing communication with the speed from less

than 300 up to over 115200 baud, and a flexible

character format.

SCI is a full-duplex UART-type asynchronous

system with standard Non Return to Zero (NRZ)

format for the transmitted/received bit. The length

of the transmitted word is 10/11 bits (1 start bit, 8/

9 data bits, 1 stop bit).

SCI is composed of three modules: Receiver,

Transmitter and Baud-Rate Generator.

13.1 SCI Receiver block

The

SCI

Receiver

block

manages

the

synchronization of the serial data stream and

stores the data characters. The SCI Receiver is

mainly composed of two sub-systems: Recovery

Buffer Block and SCDR_RX Block.

SCI receives data deriving from the RX pin and

drives the Recovery Buffer Block, which is a high-

speed shift register operating at a clock frequency

(CLOCK_RX) 16 times higher than the fixed baud

rate (CLOCK_TX). This sampling rate, higher than

the Baud Rate clock, detects the START condition,

Noise error and Frame error.

When the SCI Receiver is in IDLE status, it is

waiting for the START condition, which is obtained

with a logic level of 0, consecutive to a logic level

1. This condition is detected if, with the fixed

sampling time, a logic level 0 is sampled after three

logic levels of 1.

The recognition of the START bit forces the SCI

Receiver

Block

to

start

a

data

acquisition

sequence.

The data acquisition sequence is configured by the

apposite Configuration Register, allowing the

following data frame formats (see Figure 13.1):

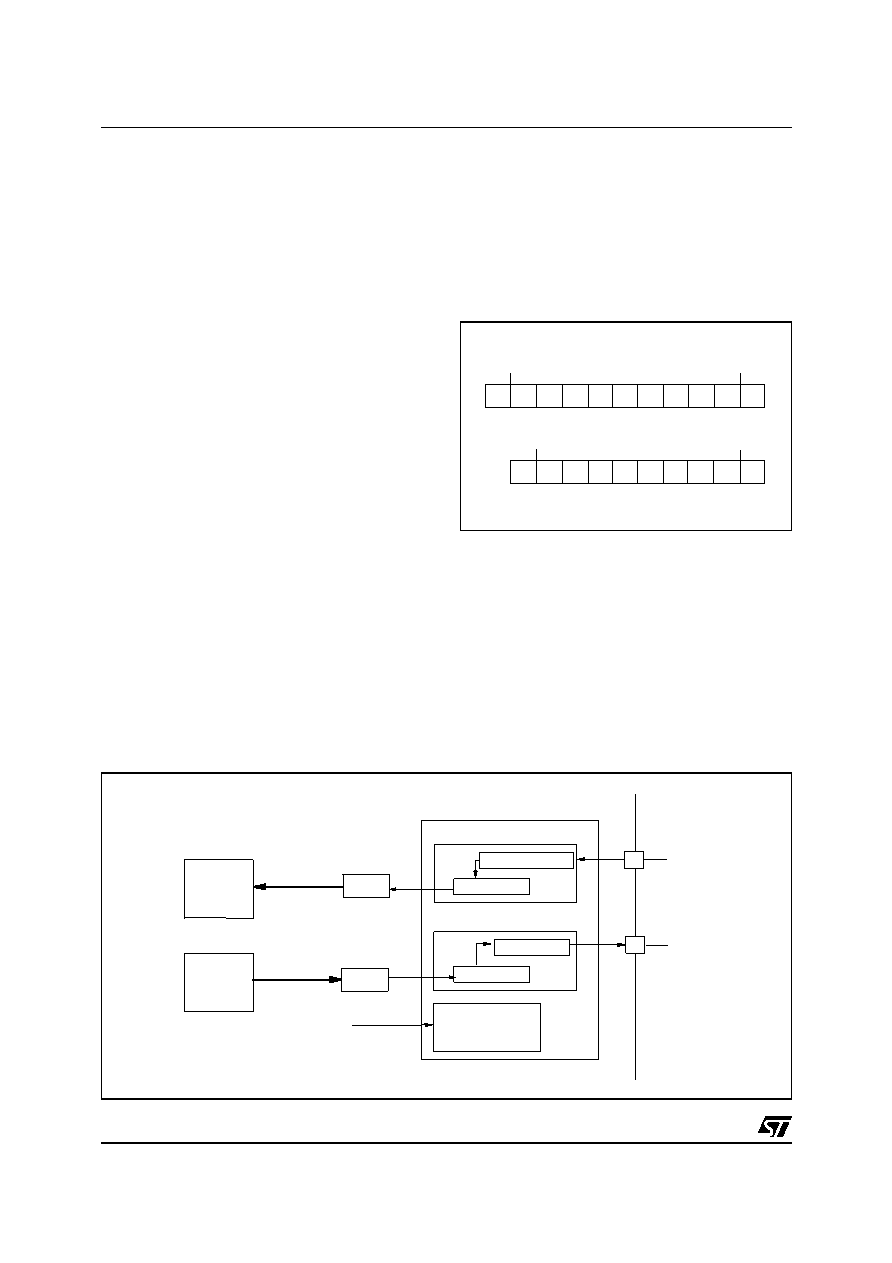

Figure 13.1 SCI transmitted word structures

s

8 bit length, 1 stop bit, no parity bit

s

8 bit length, 2 stop bit, no parity bit

s

8 bit length, 1 stop bit, with parity bit

s

9 bit length, 1 stop bit, no parity bit

The parity bit (if used) can be configured for even

or odd parity check. If the 9-bit length format is

configured, this bit is used in transmission for the

ninth bit (see below). The ninth bit received can be

read in the R8 bit of the SCI Status Register,

address 37 (035h) bit 2 (see Figure 13.3).

Figure 13.2 SCI Block Diagram

7

6

5

43

2

10

8

9

7

6

5

43

2

1

0

8

9

10

STOP

DATA

START

STOP

DATA

START

SCI

Register File

SCDR_TX

LDPR/LDPE/LDPI

Baud-Rate

Generator

LDRI

SHIFT REGISTER

SCDR_RX

RECOVERY BUFFER

RX

TX

SCI Transmitter

SCI Receiver

MCLK

Program/Data

Memory

IR

OR

相关PDF资料 |

PDF描述 |

|---|---|

| ST52F513Y1B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F513Y2B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F510Y3B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52F514Y2B6 | 8-BIT, FLASH, 24 MHz, MICROCONTROLLER, PDIP16 |

| ST52T430K3B6 | 8-BIT, OTPROM, 20 MHz, MICROCONTROLLER, PDIP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST52F513GMB6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F513GMM6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F513Y3M6 | 制造商:STMicroelectronics 功能描述: |

| ST52F513YMM6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

| ST52F514 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8-BIT INTELLIGENT CONTROLLER UNIT ICU Two Timer/PWMs, ADC, I2C, SPI, SCI |

发布紧急采购,3分钟左右您将得到回复。