- 您现在的位置:买卖IC网 > PDF目录98143 > ST6246BB6/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP56 PDF资料下载

参数资料

| 型号: | ST6246BB6/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP56 |

| 封装: | 0.600 INCH, PLASTIC, SDIP-56 |

| 文件页数: | 19/73页 |

| 文件大小: | 1806K |

| 代理商: | ST6246BB6/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页

Obsolete

Product(s)

- Obsolete

Product(s)

Obsolete

Product(s)

- Obsolete

Product(s)

26/73

ST62T46B/E46B

3.4 INTERRUPTS

The CPU can manage four Maskable Interrupt

sources, in addition to a Non Maskable Interrupt

source (top priority interrupt). Each source is asso-

ciated with a specific Interrupt Vector which con-

tains a Jump instruction to the associated interrupt

service routine. These vectors are located in Pro-

gram space (see Table 7).

When an interrupt source generates an interrupt

request, and interrupt processing is enabled, the

PC register is loaded with the address of the inter-

rupt vector (i.e. of the Jump instruction), which

then causes a Jump to the relevant interrupt serv-

ice routine, thus servicing the interrupt.

Interrupt sources are linked to events either on ex-

ternal pins, or on chip peripherals. Several events

can be ORed on the same interrupt source, and

relevant flags are available to determine which

event triggered the interrupt.

The Non Maskable Interrupt request has the high-

est priority and can interrupt any interrupt routine

at any time; the other four interrupts cannot inter-

rupt each other. If more than one interrupt request

is pending, these are processed by the processor

core according to their priority level: source #1 has

the higher priority while source #4 the lower. The

priority of each interrupt source is fixed.

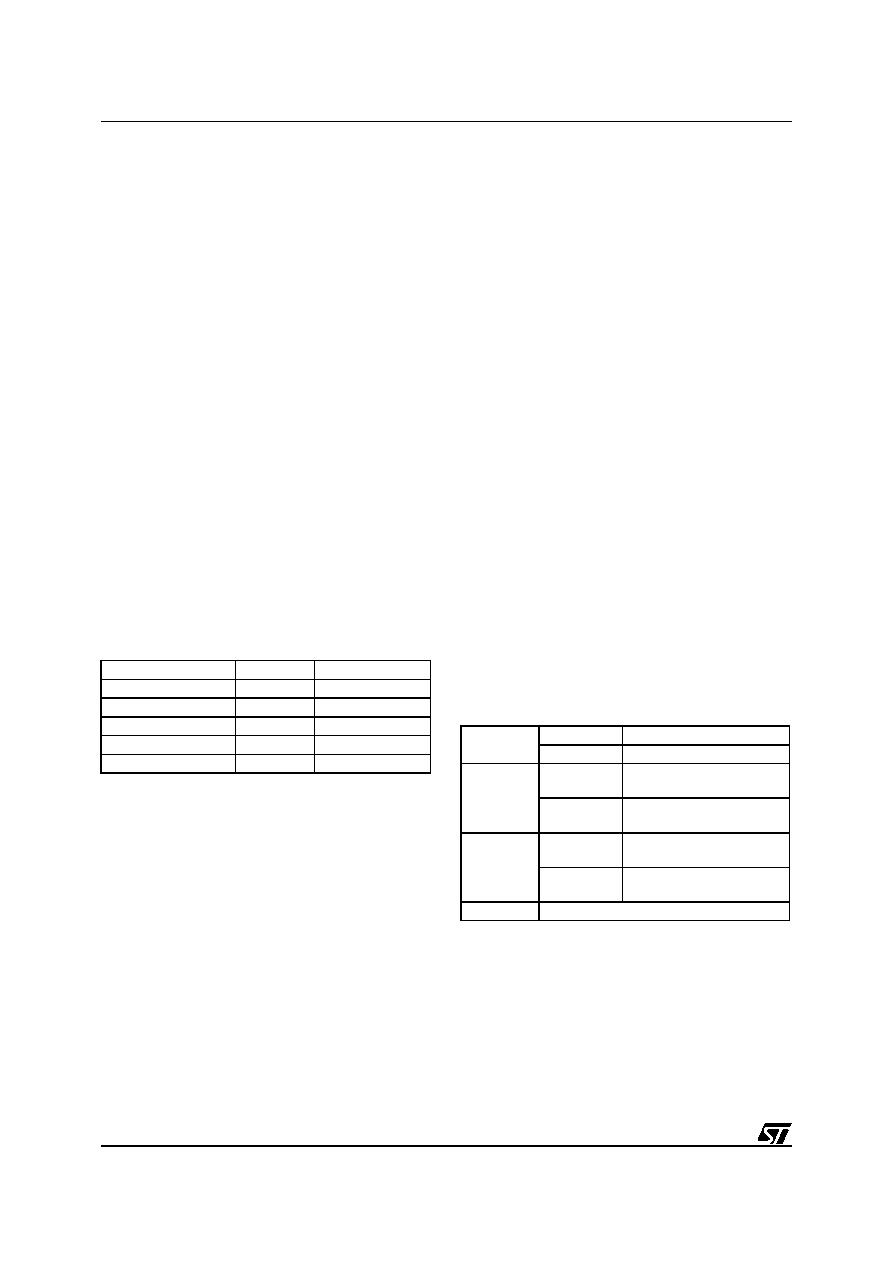

Table 7. Interrupt Vector Map

3.4.1 Interrupt request

All interrupt sources but the Non Maskable Inter-

rupt source can be disabled by setting accordingly

the GEN bit of the Interrupt Option Register (IOR).

This GEN bit also defines if an interrupt source, in-

cluding the Non Maskable Interrupt source, can re-

start the MCU from STOP/WAIT modes.

Interrupt request from the Non Maskable Interrupt

source #0 is latched by a flip flop which is automat-

ically reset by the core at the beginning of the non-

maskable interrupt service routine.

Interrupt request from source #1 can be config-

ured either as edge or level sensitive by setting ac-

cordingly the LES bit of the Interrupt Option Regis-

ter (IOR).

Interrupt request from source #2 are always edge

sensitive. The edge polarity can be configured by

setting accordingly the ESB bit of the Interrupt Op-

tion Register (IOR).

Interrupt request from sources #3 & #4 are level

sensitive.

In edge sensitive mode, a latch is set when a edge

occurs on the interrupt source line and is cleared

when the associated interrupt routine is started.

So, the occurrence of an interrupt can be stored,

until completion of the running interrupt routine be-

fore being processed. If several interrupt requests

occurs before completion of the running interrupt

routine, only the first request is stored.

Storage of interrupt requests is not available in lev-

el sensitive mode. To be taken into account, the

low level must be present on the interrupt pin when

the MCU samples the line after instruction execu-

tion.

At the end of every instruction, the MCU tests the

interrupt lines: if there is an interrupt request the

next instruction is not executed and the appropri-

ate interrupt service routine is executed instead.

Table 8. Interrupt Option Register Description

Interrupt Source

Priority

Vector Address

Interrupt source #0

1

(FFCh-FFDh)

Interrupt source #1

2

(FF6h-FF7h)

Interrupt source #2

3

(FF4h-FF5h)

Interrupt source #3

4

(FF2h-FF3h)

Interrupt source #4

5

(FF0h-FF1h)

GEN

SET

Enable all interrupts

CLEARED

Disable all interrupts

ESB

SET

Rising edge mode on inter-

rupt source #2

CLEARED

Falling edge mode on inter-

rupt source #2

LES

SET

Level-sensitive mode on in-

terrupt source #1

CLEARED

Falling edge mode on inter-

rupt source #1

OTHERS

NOT USED

相关PDF资料 |

PDF描述 |

|---|---|

| ST6260BB6 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP20 |

| ST6294B8/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP28 |

| ST62T94B8 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP28 |

| ST62E85BG1 | 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CQFP80 |

| ST62P35BQ3/XXX | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP52 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST6246B-EMU2 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:REAL TIME EMULATION DEVELOPMENT TOOLS FOR ST6 MCU FAMILY |

| ST6246-P/QFP | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:REAL TIME EMULATION DEVELOPMENT TOOLS FOR ST6 MCU FAMILY |

| ST6-24B20 | 功能描述:电源变压器 SPLIT BOBBIN HORZ MOUNT XFMR RoHS:否 制造商:Triad Magnetics 功率额定值:12 VA 初级电压额定值:115 V / 230 V 次级电压额定值:12 V / 24 V 安装风格:SMD/SMT 一次绕组:Dual Primary Winding 二次绕组:Dual Secondary Winding 长度:2.5 in 宽度:2 in 高度:1.062 in |

| ST624OB-EMU2 | 制造商:STMicroelectronics 功能描述:ST62 EMULATOR |

| ST624X | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8/16-Bit Micros |

发布紧急采购,3分钟左右您将得到回复。