- 您现在的位置:买卖IC网 > PDF目录69349 > ST6280BQ6/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP100 PDF资料下载

参数资料

| 型号: | ST6280BQ6/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP100 |

| 封装: | PLASTIC, QFP-100 |

| 文件页数: | 22/80页 |

| 文件大小: | 934K |

| 代理商: | ST6280BQ6/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页

Obsolete

Product(s)

- Obsolete

Product(s)

29/80

ST62T80B/E80B

INTERRUPTS (Cont’d)

3.4.3 Interrupt Option Register (IOR)

The Interrupt Option Register (IOR) is used to en-

able/disable the individual interrupt sources and to

select the operating mode of the external interrupt

inputs. This register is write-only and cannot be

accessed by single-bit operations.

Address: 0C8h

—

Write Only

Reset status: 00h

Bit 7, Bits 3-0 =

Unused.

Bit 6 = LES:

Level/Edge Selection bit.

When this bit is set to one, the interrupt source #1

is level sensitive. When cleared to zero the edge

sensitive mode for interrupt request is selected.

Bit 5 = ESB:

Edge Selection bit.

The bit ESB selects the polarity of the interrupt

source #2.

Bit 4 = GEN:

Global Enable Interrupt. When this bit

is set to one, all interrupts are enabled. When this

bit is cleared to zero all the interrupts (excluding

NMI) are disabled.

When the GEN bit is low, the NMI interrupt is ac-

tive but cannot cause a wake up from STOP/WAIT

modes.

This register is cleared on reset.

3.4.4 Interrupt sources

Interrupt

sources

available

on

the

ST62E80B/T80B are summarized in the Table 11

with associated mask bit to enable/disable the in-

terrupt request.

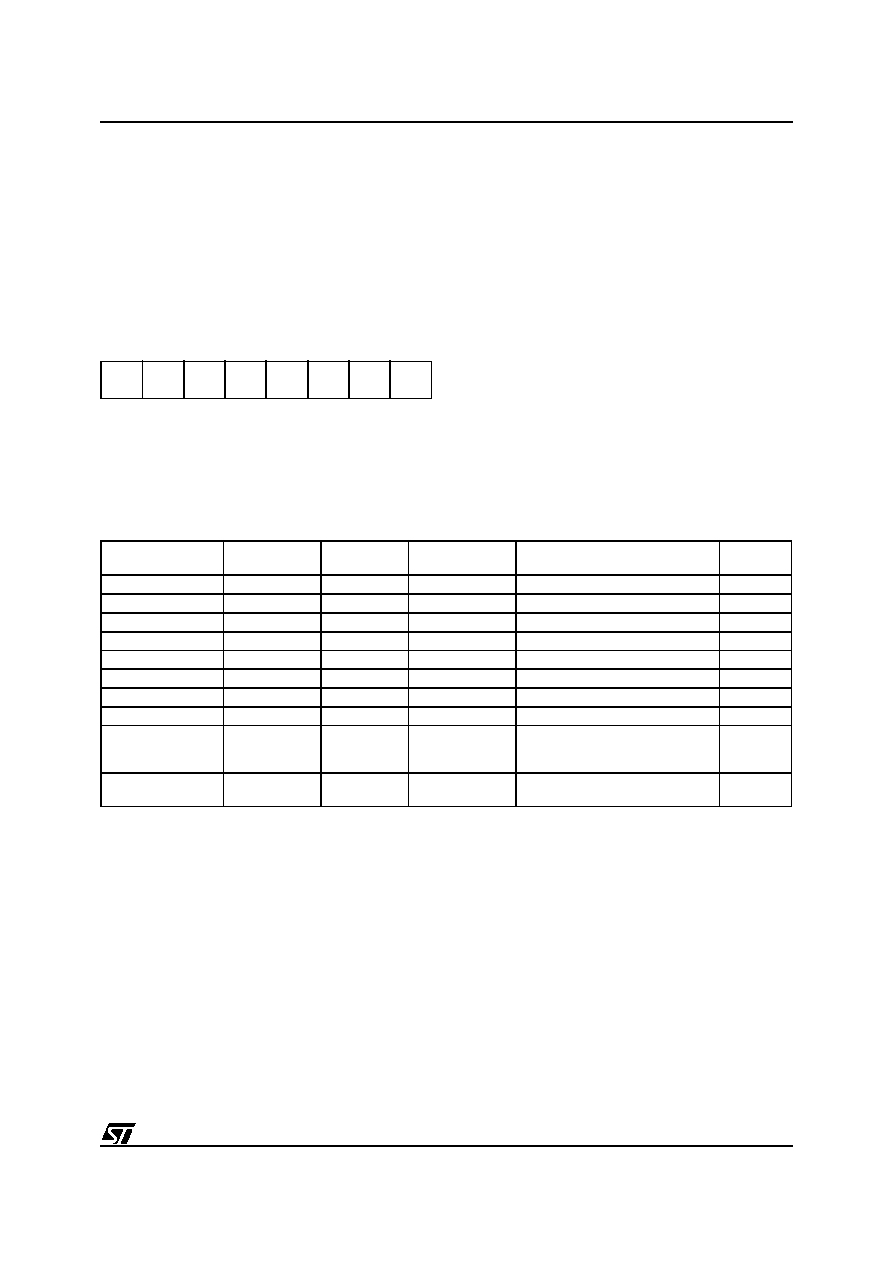

Table 11. Interrupt Requests and Mask Bits

70

-

LES

ESB

GEN

-

Peripheral

Register

Address

Register

Mask bit

Masked Interrupt Source

Interrupt

source

GENERAL

IOR

C8h

GEN

All Interrupts, excluding NMIAll

TIMER 1

TSCR1

D4h

ETI

TMZ: TIMER Overflow

source 3

A/D CONVERTER

ADCR

D1h

EAI

EOC: End of Conversion

source 4

SPI

C2h

ALL

End of Transmission

source 1

Port PAn

ORPA-DRPA

C0h-C4h

ORPAn-DRPAn

PAn pin

source 2

Port PBn

ORPB-DRPB

C1h-C5h

ORPBn-DRPBn

PBn pin

source 2

Port PCn

ORPC-DRPC

C6h-CFh

ORPCn-DRPCn

PCn pin

source 2

32kHz OSC

32OCR

DBh

EOSCI

OSCEOC

source 3

ARTIMER

ARMC

E5h

OVIE

CPIE

EIE

OVF: ARTIMER Overflow

CPF: Successful Compare

EF: Active edge on ARTIMin

source 3

UART

UARTCR

D7h

RXIEN

TXIEN

RXRDY: byte received

TXMT: byte sent

source 4

29

相关PDF资料 |

PDF描述 |

|---|---|

| ST6285Q6/XX | 8-BIT, MROM, 8.4 MHz, MICROCONTROLLER, PQFP80 |

| ST62E25CF1 | 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CDIP28 |

| ST62P15CB3 | MICROCONTROLLER, PDIP28 |

| ST6215CB3/CCC | MICROCONTROLLER, PDIP28 |

| ST62P15CM3 | MICROCONTROLLER, PDSO28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST6280-EMU2 | 功能描述:开发板和工具包 - 其他处理器 ST62 Emulator Board RoHS:否 制造商:Freescale Semiconductor 产品:Development Systems 工具用于评估:P3041 核心:e500mc 接口类型:I2C, SPI, USB 工作电源电压: |

| ST6280-P/QFP | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:REAL TIME EMULATION DEVELOPMENT TOOLS FOR ST6 MCU FAMILY |

| ST6280Q1/XX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST6280Q6/XX | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST6281T6/HEA/TR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。