- 您现在的位置:买卖IC网 > PDF目录372305 > ST62P28CM1 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS PDF资料下载

参数资料

| 型号: | ST62P28CM1 |

| 英文描述: | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| 中文描述: | 8位微控制器(MCU)的与检察官办公室。光盘。 FASTR的A / D转换器。 8位自动重加载定时器。 UART的。业务支助。安全复位和28个引脚 |

| 文件页数: | 49/84页 |

| 文件大小: | 969K |

| 代理商: | ST62P28CM1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页当前第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

49/84

ST62T28C/E28C

AUTO-RELOAD TIMER

(Cont’d)

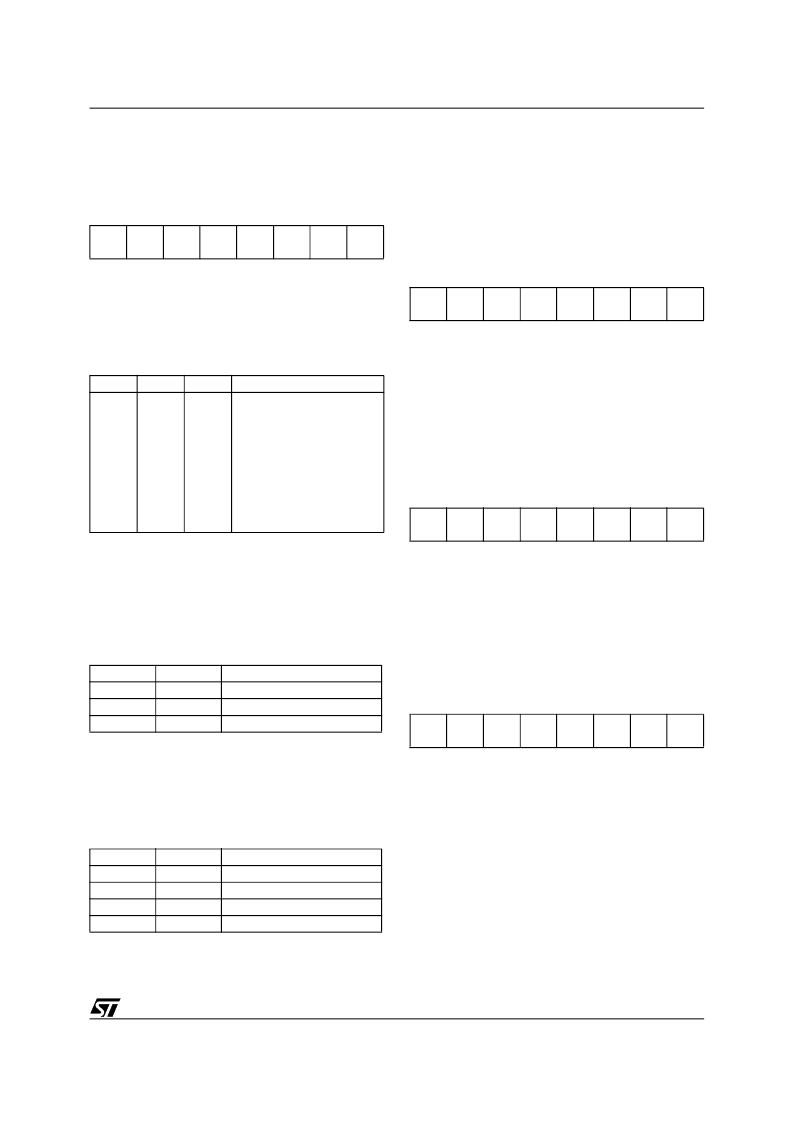

AR Status Control Register 1(ARSC1)

Address: E7h

—

Read/Write

Bist 7-5 =

PS2-PS0

:

Prescaler Division Selection

Bits 2-0.

These bits determine the Prescaler divi-

sion ratio. The prescaler itself is not affected by

these bits. The prescaler division ratio is listed in the

following table:

Table 16. Prescaler Division Ratio Selection

Bit 4 =

D4

:

Reserved

. Must be kept reset.

Bit 3-2 =

SL1-SL0

:

Timer Input Edge Control Bits 1-

0.

These bits control the edge function of the Timer

input pin for external synchronization. If bit SL0 is re-

set, edge detection is disabled; if set edge detection

is enabled. If bit SL1 is reset, the AR Timer input pin

is rising edge sensitive; if set, it is falling edge sen-

sitive.

Bit 1-0 =

CC1-CC0

:

Clock Source Select Bit 1-0.

These bits select the clock source for the AR Timer

through the AR Multiplexer. The programming of

the clock sources is explained in the following

Table

17

:

Table 17. Clock Source Selection.

AR Load Register ARLR

. The ARLR load register

is used to read or write the ARTC counter register

“on the fly” (while it is counting). The ARLR regis-

ter is not affected by system reset.

AR Load Register (ARLR)

Address: EBh

—

Read/Write

Bit 7-0 =

D7-D0

:

Load Register Data Bits.

These

are the load register data bits.

AR Reload/Capture Register

. The ARRC reload/

capture register is used to hold the auto-reload

value which is automatically loaded into the coun-

ter when overflow occurs.

AR Reload/Capture (ARRC)

Address: E9h

—

Read/Write

Bit 7-0 =

D7-D0

:

Reload/Capture Data Bits

. These

are the Reload/Capture register data bits.

AR Compare Register

. The CP compare register

is used to hold the compare value for the compare

function.

AR Compare Register (ARCP)

Address: EAh

—

Read/Write

Bit 7-0 =

D7-D0

:

Compare Data Bits

. These are

the Compare register data bits.

7

0

PS2

PS1

PS0

D4

SL1

SL0

CC1

CC0

PS2

0

0

0

0

1

1

1

1

PS1

0

0

1

1

0

0

1

1

PS0

0

1

0

1

0

1

0

1

ARPSC Division Ratio

1

2

4

8

16

32

64

128

SL1

X

0

1

SL0

0

1

1

Edge Detection

Disabled

Rising Edge

Falling Edge

CC1

0

0

1

1

CC0

0

1

0

1

Clock Source

F

int

F

int

Divided by 3

ARTIMin Input Clock

Reserved

7

0

D7

D6

D5

D4

D3

D2

D1

D0

7

0

D7

D6

D5

D4

D3

D2

D1

D0

7

0

D7

D6

D5

D4

D3

D2

D1

D0

49

相关PDF资料 |

PDF描述 |

|---|---|

| ST62P28CM3 | IC, SDRAM, DDR333, 16MX8, 6NS, CL2.5, TSOP66 |

| ST62P28CM6 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62T28CB3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62T28CB6 | 8-BIT MICROCONTROLLER |

| ST62T28CM3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P52C | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MOMTR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MPITR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MSATR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CN6/MMMTR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。