- 您现在的位置:买卖IC网 > PDF目录372305 > ST62P28CM1 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS PDF资料下载

参数资料

| 型号: | ST62P28CM1 |

| 英文描述: | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| 中文描述: | 8位微控制器(MCU)的与检察官办公室。光盘。 FASTR的A / D转换器。 8位自动重加载定时器。 UART的。业务支助。安全复位和28个引脚 |

| 文件页数: | 52/84页 |

| 文件大小: | 969K |

| 代理商: | ST62P28CM1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页

52/84

ST62T28C/E28C

4.5 U. A. R. T. (Universal Asynchronous Receiver/Transmitter)

The UART provides the basic hardware for asyn-

chronous serial communication which, combined

with an appropriate software routine, gives a serial

interface providing communication with common

baud rates (up to 76,800 Baud with an 8MHz ex-

ternal oscillator) and flexible character formats.

Operating in Half-Duplex mode only, the UART

uses a 10-bit frame or a 11-bit frame according to

the choosen MCU option. Automatic parity bit gen-

eration is software selectable in the 10-bit charac-

ter format allowing either 7 data bit + 1 parity bit, or

8 data bit transmission. Transmitted data is sent di-

rectly, while received data is buffered allowing fur-

ther data characters to be received while the data

is being read out of the receive buffer register. Data

transmit has priority over data being received.

The UART is supplied with an MCU internal clock

that is also available in WAIT mode of the processor.

4.5.1 Ports Interfacing

RXD reception line and TXD emission line are

sharing the same external pins as two I/O lines.

Therefore, UART configuration requires to set

these two I/O lines through the relevant ports reg-

isters. The I/O line common with RXD line must be

defined as input mode (with or without pull-up)

while the I/O line common with TXD line must be

defined as output mode (Push-pull or open drain).

In the 11-bit character format option, the transmit-

ted data is inverted and can therefore use a single

transistor buffering stage. Defined as input, the

RXD line can be read at any time as an I/O line

during the UART operation. The TXD pin follows I/

O port registers value when UARTOE bit is

cleared, which means when no serial transmission

is in progress. As a consequence, a permanent

high level has to be written onto the I/O port in or-

der to achieve a proper stop condition on the TXD

line when no transmission is active.

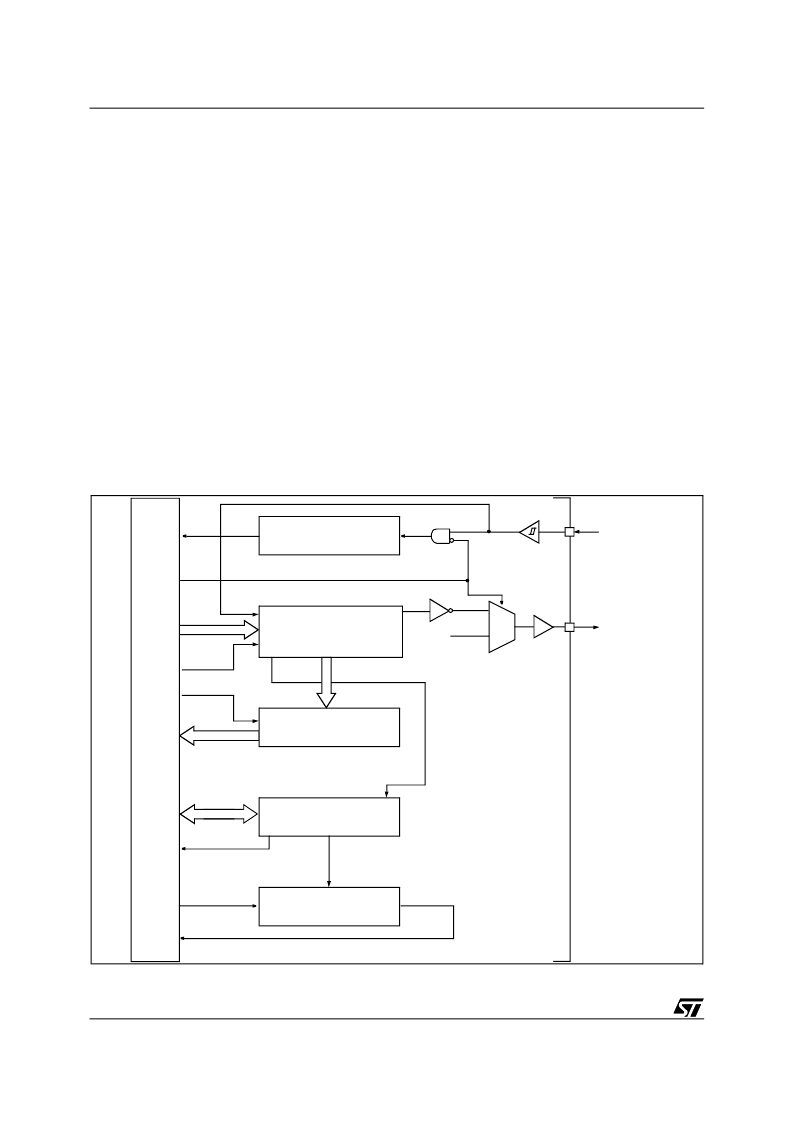

Figure 30. UART Block Diagram

C

T

START

DETECTOR

DATA SHIFT

REGISTER

D8 D7 D6 D5 D4 D3 D2 D1 D0

CONTROL REGISTER

BAUD RATE

RECEIVE BUFFER

REGISTER

PROGRAMMABLE

DIVIDER

DIN

DOUT

D8

BAUD RATE x 8

WRITE

READ

RXD1

TXD1

UARTOE

RX and TX

INTERRUPTS

TXD

DR

0

MUX

1

f

OSC

VR02009

52

相关PDF资料 |

PDF描述 |

|---|---|

| ST62P28CM3 | IC, SDRAM, DDR333, 16MX8, 6NS, CL2.5, TSOP66 |

| ST62P28CM6 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62T28CB3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62T28CB6 | 8-BIT MICROCONTROLLER |

| ST62T28CM3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P52C | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MOMTR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MPITR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CM6/MSATR | 制造商:STMicroelectronics 功能描述: |

| ST62P62CN6/MMMTR | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。