- 您现在的位置:买卖IC网 > PDF目录69350 > ST62P65CM3/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO28 PDF资料下载

参数资料

| 型号: | ST62P65CM3/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO28 |

| 封装: | 0.300 INCH, PLASTIC, SOP-28 |

| 文件页数: | 52/86页 |

| 文件大小: | 970K |

| 代理商: | ST62P65CM3/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页

56/86

ST62T55C ST62T65C/E65C

SERIAL PERIPHERAL INTERFACE SPI (Cont’d)

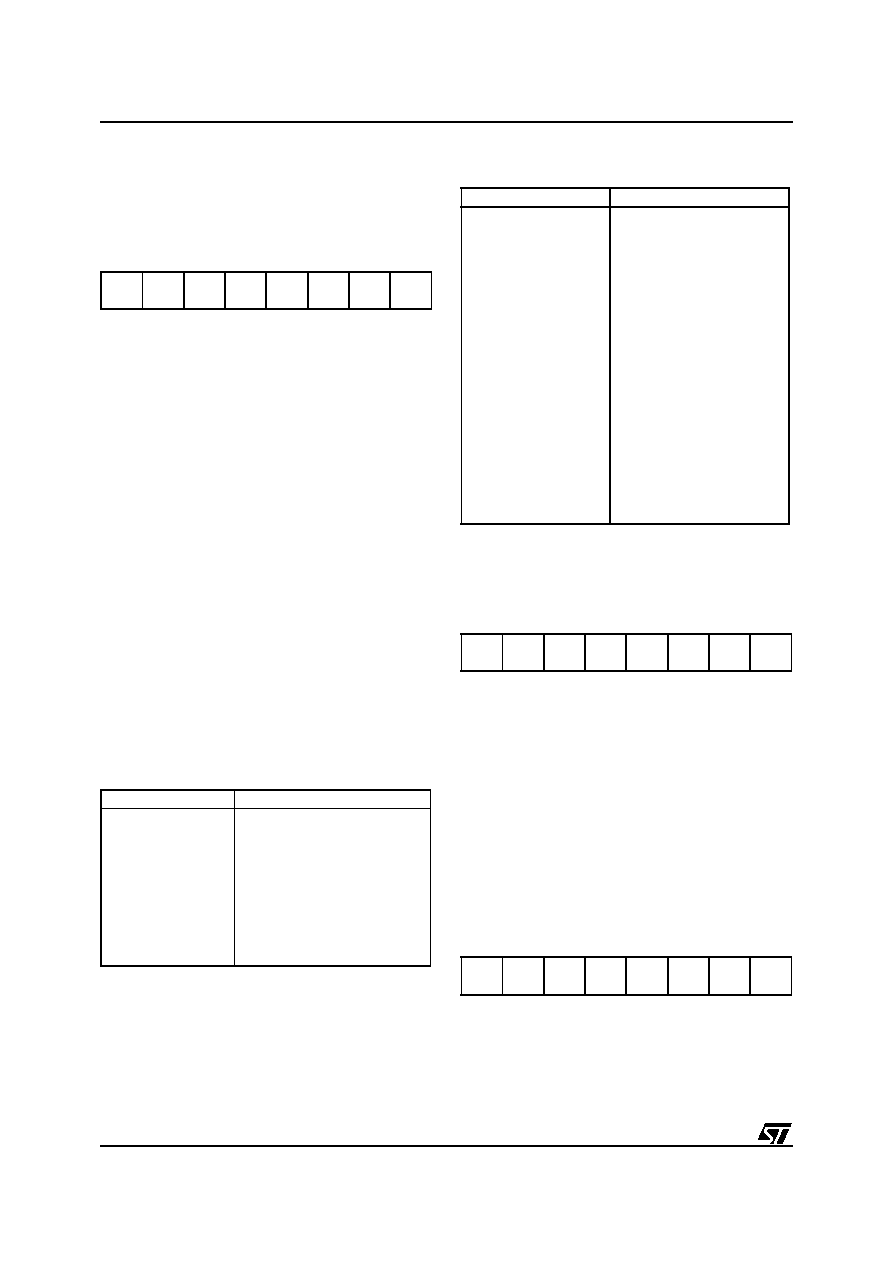

SPI DIV Register (DIV)

Address: E1h

—

Read/Write

Reset status: 00h

The SPIDIV register defines the transmission rate

and frame format and contains the interrupt flag.

Bits CD0-CD2, DIV3-DIV6 are read/write while

SPINT can be read and cleared only. Write access

is not allowed if SPRUN in the MOD register is set.

Bit 7 = SPINT:

Interrupt Flag. If SPIE bit=1, SPINT

is automatically set to one by the SPI at the end of

a transmission or reception and an interrupt re-

quest can be generated depending on the state of

the interrupt mask bit in the MOD control register.

This bit is write and read and must be cleared by

user software at the end of the interrupt service

routine.

Bit 6-3 = DIV6-DIV3:

Burst Mode Bit Clock Period

Selection. Define the number of shift register bits

that are transmitted or received in a frame. The

available selections are listed in Table 17. The

normal maximum setting is 8 bits, since the shift

register is 8 bits wide. Note that by setting a great-

er number of bits, in conjunction with the SPIN bit

in the MOD register, unwanted data bits may be fil-

tered from the data stream.

Bit 2-0 = CD2-CD0:

Base/Bit Clock Rate Selec-

tion. Define the division ratio between the core

clock (fINT divided by 13) and the clock supplied to

the Shift Register in Master mode.

Table 16. Base/Bit Clock Ratio Selection

Note: For example, when an 8MHz CPU clock is

used, asynchronous operation at 9600 Baud is

possible (8MHz/13/64). Other Baud rates are

available by proportionally selecting division fac-

tors depending on CPU clock frequency.

Data setup time on Sin is typically 250ns min, while

data hold time is typically 50ns min.

SPI Data/Shift Register (SPIDSR)

Address: E0h

—

Read/Write

Reset status: XXh

SPIDSR is read/write, however write access is not

allowed if the SPRUN bit of Mode Control register

is set to one.

Data is sampled into SPDSR on the SCK edge de-

termined by the CPOL and CPHA bits. The affect

of these setting is shown in the following diagrams.

The Shift Register transmits and receives the Most

Significant Bit first.

Bit 7-0 = DSR7-DSR0:

Data Bits. These are the

SPI shift register data bits.

Miscellaneous Register (MISCR)

Address: DDh

—

Write only

Reset status: xxxxxxxb

Bit 7-1 = D7-D1:

Reserved.

Bit 0 = D0:

Bit 0. This bit, when set, selects the

Sout pin as the SPI output line. When this bit is

cleared, Sout acts as a standard I/O line.

70

SPINT

DOV6

DIV5

DIV4

DIV3

CD2

CD1

CD0

CD2-CD0

Divide Ratio (decimal)

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Divide by 1

Divide by 2

Divide by 4

Divide by 8

Divide by 16

Divide by 32

Divide by 64

Divide by 256

DIV6-DIV3

Number of bits sent

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Reserved (not to be used)

1

2

3

4

5

6

7

8

9

10

11

Refer to the

12

description of the

13

DIV6-DIV3 bits in

14

the DIV Register

15

70

D7

D6

D5

D4

D3

D2

D1

D0

70

---

-

D0

相关PDF资料 |

PDF描述 |

|---|---|

| ST62T03CB6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP16 |

| ST62T01CB1 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDIP16 |

| ST62P00CB3/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP16 |

| ST62T00CM6 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO16 |

| ST62T00CM1 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO16 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST62P65CM6/MRYTR | 制造商:STMicroelectronics 功能描述: |

| ST62P65CM6/RAL/TR | 制造商:STMicroelectronics 功能描述: |

| ST62P65CM6/RAP/TR | 制造商:STMicroelectronics 功能描述: |

| ST62T00CB6 | 功能描述:8位微控制器 -MCU OTP EPROM 1K No Intf RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST62T00CB6 | 制造商:STMicroelectronics 功能描述:IC 8BIT MCU OTP 1K 62T00 DIP16 |

发布紧急采购,3分钟左右您将得到回复。