- 您现在的位置:买卖IC网 > PDF目录372305 > ST62T94B8 Telecommunication IC PDF资料下载

参数资料

| 型号: | ST62T94B8 |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成电路 |

| 文件页数: | 44/82页 |

| 文件大小: | 870K |

| 代理商: | ST62T94B8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

44/82

ST62T18C/E18C

TIMER

(Cont’d)

4.2.3 Application Notes

TMZ is set when the counter reaches zero; howev-

er, it may also be set by writing 00h in the TCR

register or by setting bit 7 of the TSCR register.

The TMZ bit must be cleared by user software

when servicing the timer interrupt to avoid unde-

sired interrupts when leaving the interrupt service

routine. After reset, the 8-bit counter register is

loaded with 0FFh, while the 7-bit prescaler is load-

ed with 07Fh, and the TSCR register is cleared.

This means that the Timer is stopped (PSI=“0”)

and the timer interrupt is disabled.

If the Timer is programmed in output mode, the

DOUT bit is transferred to the TIMER pin when

TMZ is set to one (by software or due to counter

decrement). When TMZ is high, the latch is trans-

parent and DOUT is copied to the timer pin. When

TMZ goes low, DOUT is latched.

A write to the TCR register will predominate over

the 8-bit counter decrement to 00h function, i.e. if a

write and a TCR register decrement to 00h occur

simultaneously, the write will take precedence,

and the TMZ bit is not set until the 8-bit counter

reaches 00h again. The values of the TCR and the

PSC registers can be read accurately at any time.

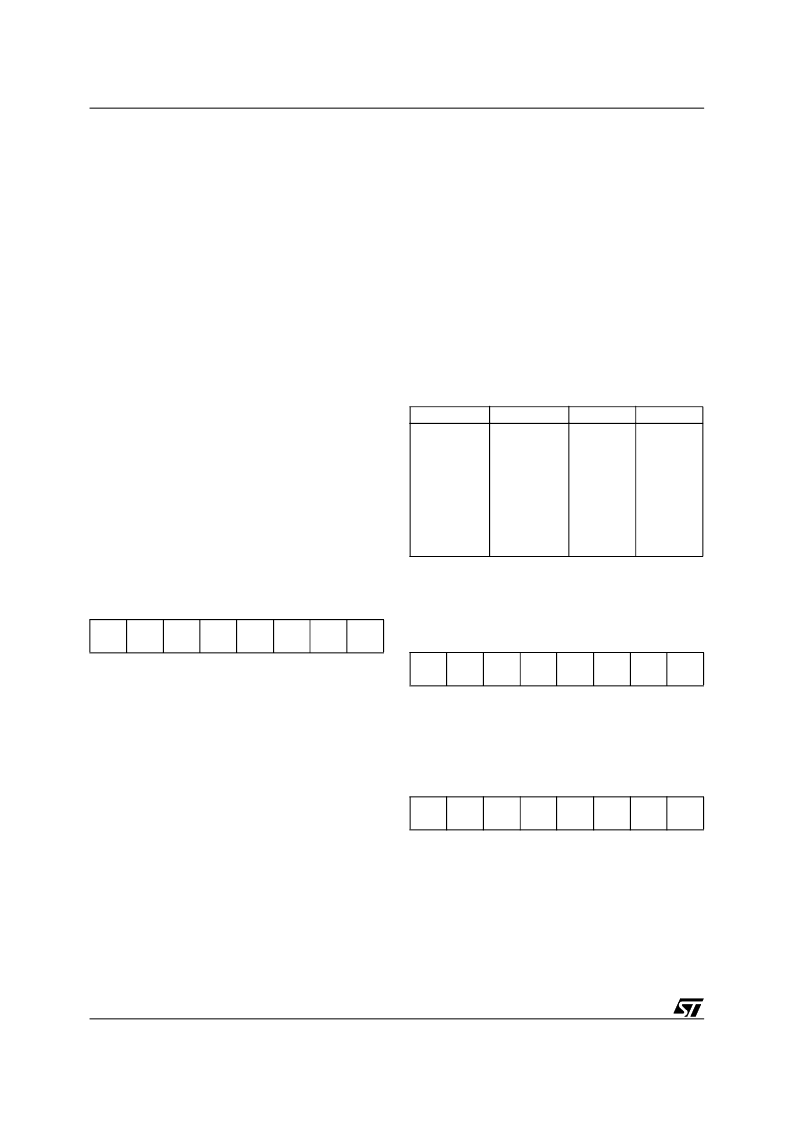

4.2.4 Timer Registers

Timer Status Control Register (TSCR)

Address: 0D4h

—

Read/Write

Bit 7 =

TMZ

:

Timer Zero bit

A low-to-high transition indicates that the timer

count register has decrement to zero. This bit must

be cleared by user software before starting a new

count.

Bit 6 =

ETI

:

Enable Timer Interrupt

When set, enables the timer interrupt request. If

ETI=0 the timer interrupt is disabled. If ETI=1 and

TMZ=1 an interrupt request is generated.

Bit 5 =

TOUT

:

Timers

Output Control

When low, this bit selects the input mode for the

TIMER pin. When high the output mode is select-

ed.

Bit 4 =

DOUT

:

Data Output

Data sent to the timer output when TMZ is set high

(output mode only). Input mode selection (input

mode only).

Bit 3 =

PSI

:

Prescaler Initialize Bit

Used to initialize the prescaler and inhibit its count-

ing. When PSI=“0” the prescaler is set to 7Fh and

the counter is inhibited. When PSI=“1” the prescal-

er is enabled to count downwards. As long as

PSI=“0” both counter and prescaler are not run-

ning.

Bit 2, 1, 0 =

PS2, PS1, PS0

:

Prescaler Mux. Se-

lect.

These bits select the division ratio of the pres-

caler register.

Table 15. Prescaler Division Factors

Timer Counter Register TCR

Address: 0D3h

—

Read/Write

Bit 7-0 =

D7-D0

:

Counter Bits.

Prescaler Register PSC

Address: 0D2h

—

Read/Write

Bit 7 =

D7

: Always read as “0”.

Bit 6-0 =

D6-D0

: Prescaler Bits.

7

0

TMZ

ETI

TOUT

DOUT

PSI

PS2

PS1

PS0

PS2

0

0

0

0

1

1

1

1

PS1

0

0

1

1

0

0

1

1

PS0

0

1

0

1

0

1

0

1

Divided by

1

2

4

8

16

32

64

128

7

0

D7

D6

D5

D4

D3

D2

D1

D0

7

0

D7

D6

D5

D4

D3

D2

D1

D0

44

相关PDF资料 |

PDF描述 |

|---|---|

| ST62T94M8 | Telecommunication IC |

| ST6228C | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62E28CF1 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62P28CB1 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62P28CB3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST63/69/23 | 制造商:Block 功能描述:Control panel transformer, 63VA, 230V |

| ST6-30 | 制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER |

| ST630/69/23 | 制造商:Block USA Inc. 功能描述:Control panel transformer, 630VA, 230V |

| ST6306 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST6307 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。