- 您现在的位置:买卖IC网 > PDF目录372305 > ST62T94M8 Telecommunication IC PDF资料下载

参数资料

| 型号: | ST62T94M8 |

| 英文描述: | Telecommunication IC |

| 中文描述: | 通信集成电路 |

| 文件页数: | 55/82页 |

| 文件大小: | 870K |

| 代理商: | ST62T94M8 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页当前第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页

55/82

ST62T18C/E18C

U. A. R. T

(Cont’d)

4.5.4 Data Reception

The UART continuously looks for a falling edge on

the input pin whenever a transmission is not ac-

tive. Once an edge is detected it waits 1 bit time (8

states) to accommodate the Start bit, and then as-

sembles the following serial data stream into the

data register. First 8 bit are stored into the UART

Data Register, while the additionnal 9th bit is

stored into the LSB of the UART Control Register

in case of the 11-bit frame MCU option has been

selected. When the 10-bit frame option is selected,

the parity of the 8 received bit is automatically writ-

ten into the LSB of the UART Control Register

(PTYEN bit).

After all bit have been received, the Receiver waits

for the duration of one bit (for the Stop bit) and

then transfers the received data into the buffer reg-

ister, allowing a following character to be received.

The interrupt flag RXRDY is set to 1 as the data is

transferred to the buffer register and, if enabled,

will generate an interrupt.

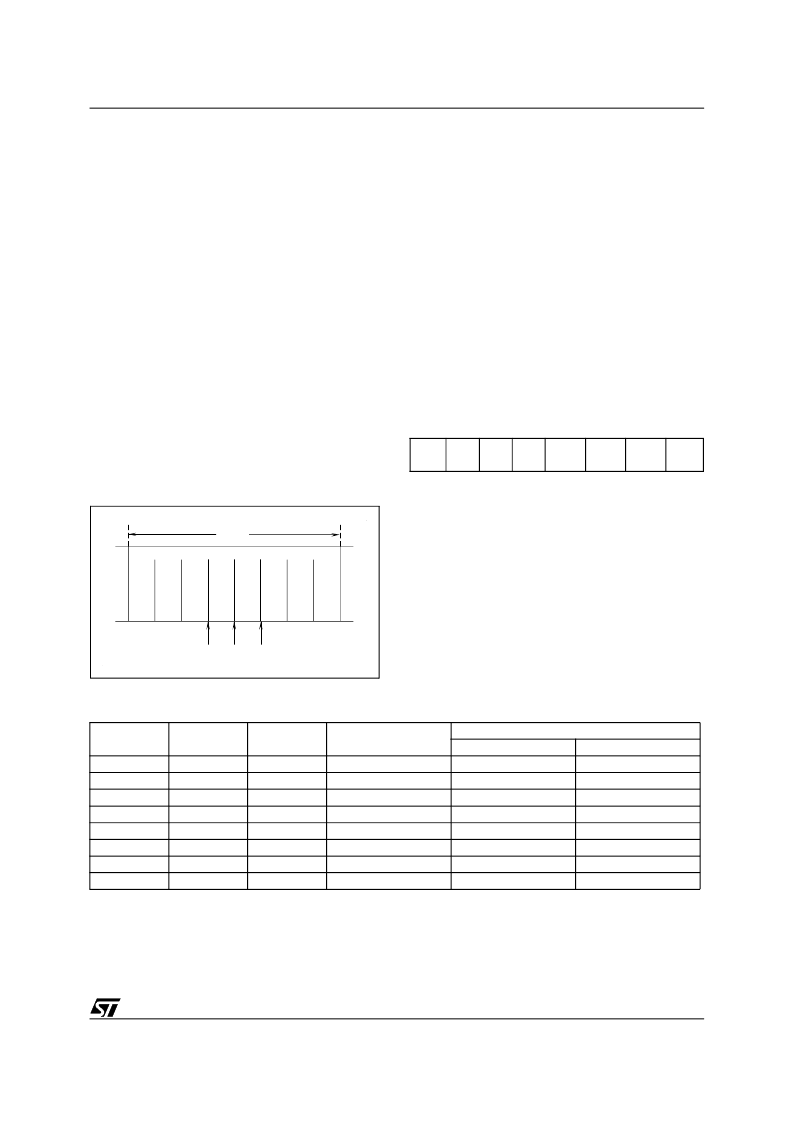

Figure 33. Data Sampling Points

If a transmission is started during the course of a

reception, the transmission takes priority and the

reception is stopped to free the resources for the

transmission. This implies that a handshaking sys-

tem must be implemented, as polling of the UART

to detect reception is not available.

4.5.5 Interrupt Capabilities

Both reception and transmission processes can in-

duce interrupt to the core as defined in the inter-

rupt section. These interrupts are enabled by set-

ting TXIEN and RXIEN bit in the UARTCR register,

and TXMT and RXRDY flags are set accordingly

to the interrupt source.

4.5.6 Registers

UART Data Register (UARTDR)

Address: D6h, Read/Write

Bit7-Bit0.

UART data bits

. A write to this register

loads the data into the transmit shift register and

triggers the start of transmission. In addition this

resets the transmit interrupt flag TXMT. A read of

this register returns the data from the Receive

buffer. If the automatic even parity computation is

set (Bit PTYEN set), D7 must be cleared to 0 be-

fore transmission. Only the 7 LSB D0..D6 contain

the data to be sent.

Warning

. No Read/Write Instructions may be

used with this register as both transmit and receive

share the same address

Table 19. Baudrate Selection

VR02010

1 BIT

0

1

2

3

4

5

6

7

8

SAMPLES

7

0

D7

D6

D5

D4

D3

D2

D1

D0

BR2

BR1

BR0

f

INT

Division

Baud Rate

f

INT

= 8MHz

1200

2400

4800

9600

19200

31200

38400

76800

f

INT

= 4MHz

600

1200

2400

4800

9600

15600

19200

38400

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

6.656

3.328

1.664

832

416

256

208

104

55

相关PDF资料 |

PDF描述 |

|---|---|

| ST6228C | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62E28CF1 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62P28CB1 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62P28CB3 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

| ST62P28CB6 | 8-BIT MICROCONTROLLER ( MCU ) WITH OTP. ROM. FASTR A/D CONVERTER. 8-BIT AUTO-RELOAD TIMER. UART. OSG. SAFE RESET AND 28 PINS |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST63/69/23 | 制造商:Block 功能描述:Control panel transformer, 63VA, 230V |

| ST6-30 | 制造商:SUPERWORLD 制造商全称:Superworld Electronics 功能描述:POWER TRANSFORMER |

| ST630/69/23 | 制造商:Block USA Inc. 功能描述:Control panel transformer, 630VA, 230V |

| ST6306 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| ST6307 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。