- 您现在的位置:买卖IC网 > PDF目录385871 > ST70135A (意法半导体) ASCOTTM DMT TRANSCEIVER PDF资料下载

参数资料

| 型号: | ST70135A |

| 厂商: | 意法半导体 |

| 英文描述: | ASCOTTM DMT TRANSCEIVER |

| 中文描述: | ASCOTTM大唐收发器 |

| 文件页数: | 19/29页 |

| 文件大小: | 198K |

| 代理商: | ST70135A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页当前第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页

ST70135A

19/29

DIGITAL INTERFACE

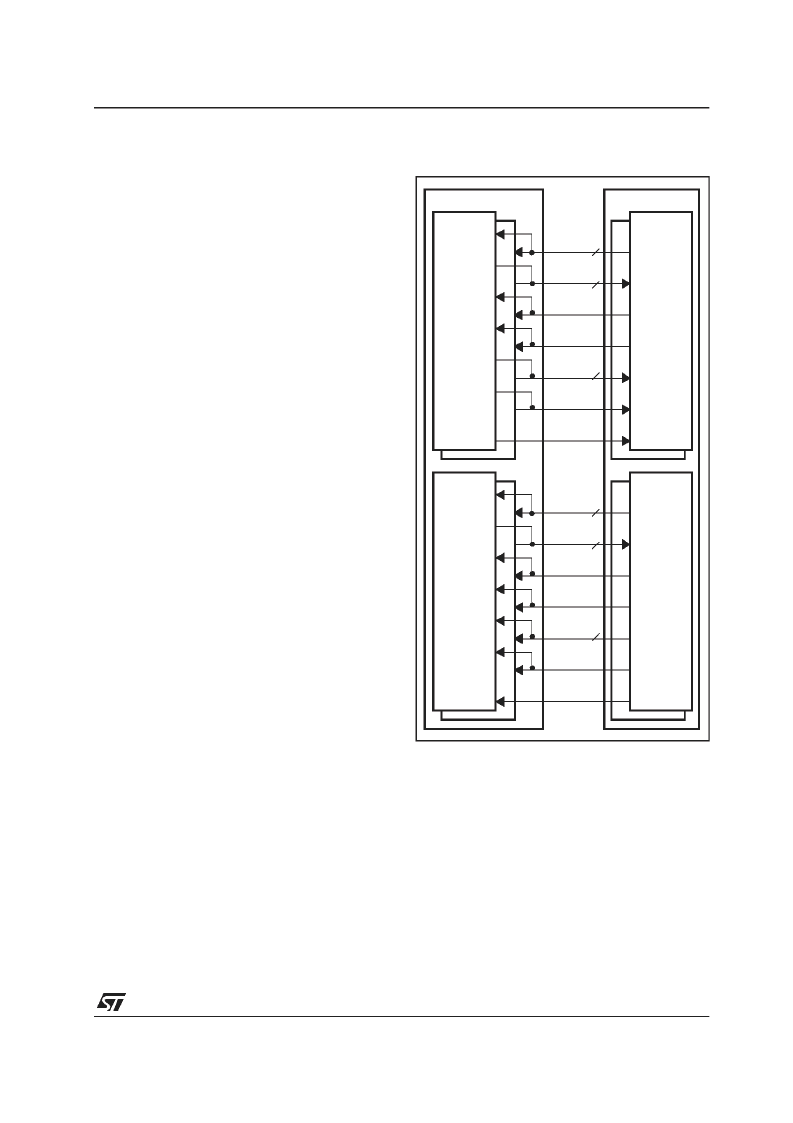

Utopia Level 2 Interface

The ATM forum takes the ATM layer chip as a

reference. It defines the direction from ATM to

physical layer as the Transmit direction. The

direction from physical layer to ATM is the Receive

direction. Figure 17 shows the interconnection

between ATM and PHY layer devices, the optional

signals are not supported and not shown.

The UTOPIA interface transfers one byte in a

single clock cycle, as a result cells are transferred

in 53 clock cycles.Both transmit and receive

interfaces are synchronized on clocks generated

by the ATM layerchip, and no specific relationship

between Receive and Transmit clock is assumed,

they must be regarded as mutually asynchronous

clocks. Flowcontrol signals are available to match

the bandwidth constraints of the physical layer

and the ATM layer. The UTOPIA level 2 supports

point to multipoint configurations by introducing

on addressing capability and

distinction between polling and selecting a device:

– The ATM chip polls a specific physical layer chip

by putting its address on the address bus when

the Enb* line is asserted. The addressed physi-

cal layer answers the next cycle via theClav line

reflecting its status at that time.

– The ATM chip selects a specific physical layer

by putting its address on the address bus when

the Enb* line is deasserted and asserting the

Enb* line on the next cycle. The addressed

physical layer chip will be the target orsource of

the next cell transfer (see Figure 17).

by making a

Utopia Level 2 Signals

The physical chip sends cell data towards the

ATM layer chip. The ATM layer chip polls the

status ofthe fifo of the physical layer chip. The cell

exchange proceeds like:

a) The physical layer chip signals the availability

of a cell by asserting RxClav when polled by

the ATM chip.

b) The ATM chips selects a physical layer chip,

then starts the transfer by asserting RxEnb*.

c)

If the physical layer chip has data to send, it

puts them on the RxData line the cycle after it

sampled RxEnb* active. It also advances the

offset in the cell. If the data transferred is the

first byte of a cell, RxSOC is 1b at the time of

the data transfer, 0b otherwise.

d)

The ATM chip accepts the data when they are

available. If RxSOC was 1b during the transfer,

it resets its internal offset pointer to thevalue 1,

otherwise it advances the offset in the cell.

ST70135A Utopia Level 2 MPHY Operation

Utopia level 2 MPHY operation can be done by

various

interface

schemes.

supports only the required mode, this mode is

referred to as ”Operation with 1 TxClav and 1

RxClav”.

The

ST70135A

PHY Device Identification

The ST70135A holds 2 PHY layer Utopia ports,

one is dedicated to the fast data channel, the

other one to the interleaved data channel. The

associated PHY address is specified by the

PHY_ADDR_x fields in the Utopia PHY address

register.

Figure 17 :

Signal at Utopia Level 2 Interface

PHY

RECEIVE

RxADDR

RxCLAV

RxENB*

RxCLK

RxDATA

RxSOC

PHY

ATM

8

5

RxREF*

ATM

RECEIVE

PHY

TRANSMIT

TxADDR

TxCLAV

TxENB*

TxCLK

TxDATA

TxSOC

8

5

TxREF*

ATM

TRANSMIT

1

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST70136 | CPE ADSL ANALOG FRONT END |

| ST70136B | CPE ADSL ANALOG FRONT END |

| ST70136G | CPE ADSL ANALOG FRONT END |

| ST70137 | UNICORNTM PCI & USB CONTROLLERLESS ADSL DMT TRANSCEIVER |

| ST70137TQFP | UNICORNTM PCI & USB CONTROLLERLESS ADSL DMT TRANSCEIVER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST70136 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136B | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136G | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:CPE ADSL ANALOG FRONT END |

| ST70136Q | 功能描述:射频无线杂项 ADSL Analg Front-End RoHS:否 制造商:Texas Instruments 工作频率:112 kHz to 205 kHz 电源电压-最大:3.6 V 电源电压-最小:3 V 电源电流:8 mA 最大功率耗散: 工作温度范围:- 40 C to + 110 C 封装 / 箱体:VQFN-48 封装:Reel |

| ST70137 | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。