- 您现在的位置:买卖IC网 > PDF目录98144 > ST72324BLJ2TA/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | ST72324BLJ2TA/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | 10 X 10 MM, TQFP-44 |

| 文件页数: | 56/151页 |

| 文件大小: | 1209K |

| 代理商: | ST72324BLJ2TA/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页当前第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页

ST72F324L, ST72324BL

149/151

15.1.6 SCI Wrong Break duration

Description

A single break character is sent by setting and re-

setting the SBK bit in the SCICR2 register. In

some cases, the break character may have a long-

er duration than expected:

- 20 bits instead of 10 bits if M=0

- 22 bits instead of 11 bits if M=1.

In the same way, as long as the SBK bit is set,

break characters are sent to the TDO pin. This

may lead to generate one break more than expect-

ed.

Occurrence

The occurrence of the problem is random and pro-

portional to the baudrate. With a transmit frequen-

cy

of

19200

baud

(fCPU=8MHz

and

SCI-

BRR=0xC9), the wrong break duration occurrence

is around 1%.

Workaround

If this wrong duration is not compliant with the

communication protocol in the application, soft-

ware can request that an Idle line be generated

before the break character. In this case, the break

duration is always correct assuming the applica-

tion is not doing anything between the idle and the

break. This can be ensured by temporarily disa-

bling interrupts.

The exact sequence is:

- Disable interrupts

- Reset and Set TE (IDLE request)

- Set and Reset SBK (Break Request)

- Re-enable interrupts

15.2 ROM DEVICES ONLY

15.2.1 I/O Port A and F Configuration

When using an external quartz crystal or ceramic

resonator, the fOSC2 clock may be disturbed be-

cause the device goes into reserved mode control-

led by Port A and F.

This happens with either one of the following con-

figurations:

PA3=0, PF4=1, PF1=0 when the PLL option is dis-

abled and PF0 is toggling

PA3=0, PF4=1, PF1=0, PF0=1 when the PLL op-

tion is enabled

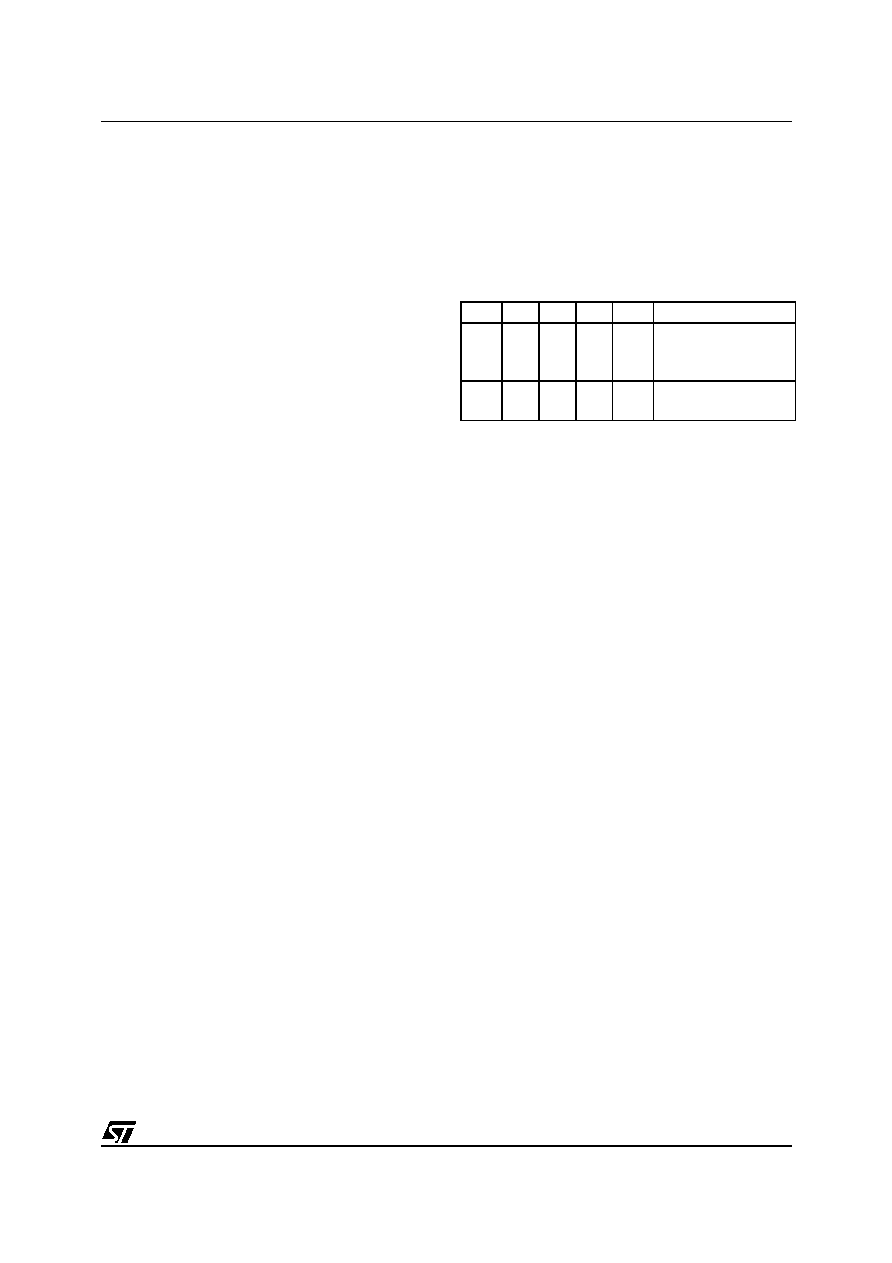

This is detailed in the following table:

As a consequence, for cycle-accurate operations,

these configurations are prohibited in either input

or output mode.

Workaround:

To avoid this occurring, it is recommended to con-

nect one of these pins to GND (PF4 or PF0) or

VDD (PA3 or PF1).

15.3 FLASH DEVICES ONLY

15.3.1 Timer A Restrictions in Flash Devices

In Flash devices, Timer A functionality has the fol-

lowing restrictions:

– TAOC2HR and TAOC2LR registers are write

only

– Input Capture 2 is not implemented

– The corresponding interrupts cannot be used

(ICF2, OCF2 forced by hardware to zero)

15.3.2 External clock source with PLL

External clock source is not supported with the

PLL enabled.

15.3.3 39-Pulse ICC Entry Mode

ICC mode entry using ST7 application clock (39

pulses) is not supported. External clock mode

must be used (36 pulses). Refer to the ST7 Flash

Programming Reference Manual.

PLL PA3 PF4 PF1 PF0 Clock Disturbance

OFF

0

1

0

Tog-

gling

Max. 2 clock cycles

lost at each rising or

falling edge of PF0

ON

0

1

0

1

Max. 1 clock cycle

lost out of every 16

1

相关PDF资料 |

PDF描述 |

|---|---|

| ST72324BLK2BA/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

| ST72345C4T6 | MICROCONTROLLER, PQFP48 |

| ST72344K4T6 | MICROCONTROLLER, PQFP32 |

| ST72344S2T6TR | MICROCONTROLLER, PQFP44 |

| ST72344S4T6 | MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72324BLJ4 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3V RANGE 8-BIT MCU WITH 8 TO 32K FLASH/ROM, 10-BIT ADC, 4 TIMERS, SPI, SCI INTERFACE |

| ST72324BLJ4B1 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3V range 8-bit MCU with 8 to 32K Flash/ROM, 10-bit ADC, 4 timers, SPI, SCI interface |

| ST72324BLJ4B5 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3V range 8-bit MCU with 8 to 32K Flash/ROM, 10-bit ADC, 4 timers, SPI, SCI interface |

| ST72324BLJ4B6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3V range 8-bit MCU with 8 to 32K Flash/ROM, 10-bit ADC, 4 timers, SPI, SCI interface |

| ST72324BLJ4BA | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:3V RANGE 8-BIT MCU WITH 8 TO 32K FLASH/ROM, 10-BIT ADC, 4 TIMERS, SPI, SCI INTERFACE |

发布紧急采购,3分钟左右您将得到回复。