- 您现在的位置:买卖IC网 > PDF目录136617 > ST72511R6T1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | ST72511R6T1/XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| 封装: | 14 X 14 MM, TQFP-64 |

| 文件页数: | 74/164页 |

| 文件大小: | 1043K |

| 代理商: | ST72511R6T1/XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页

ST72311R, ST72511R, ST72512R, ST72532R

17/164

DATA EEPROM (Cont’d)

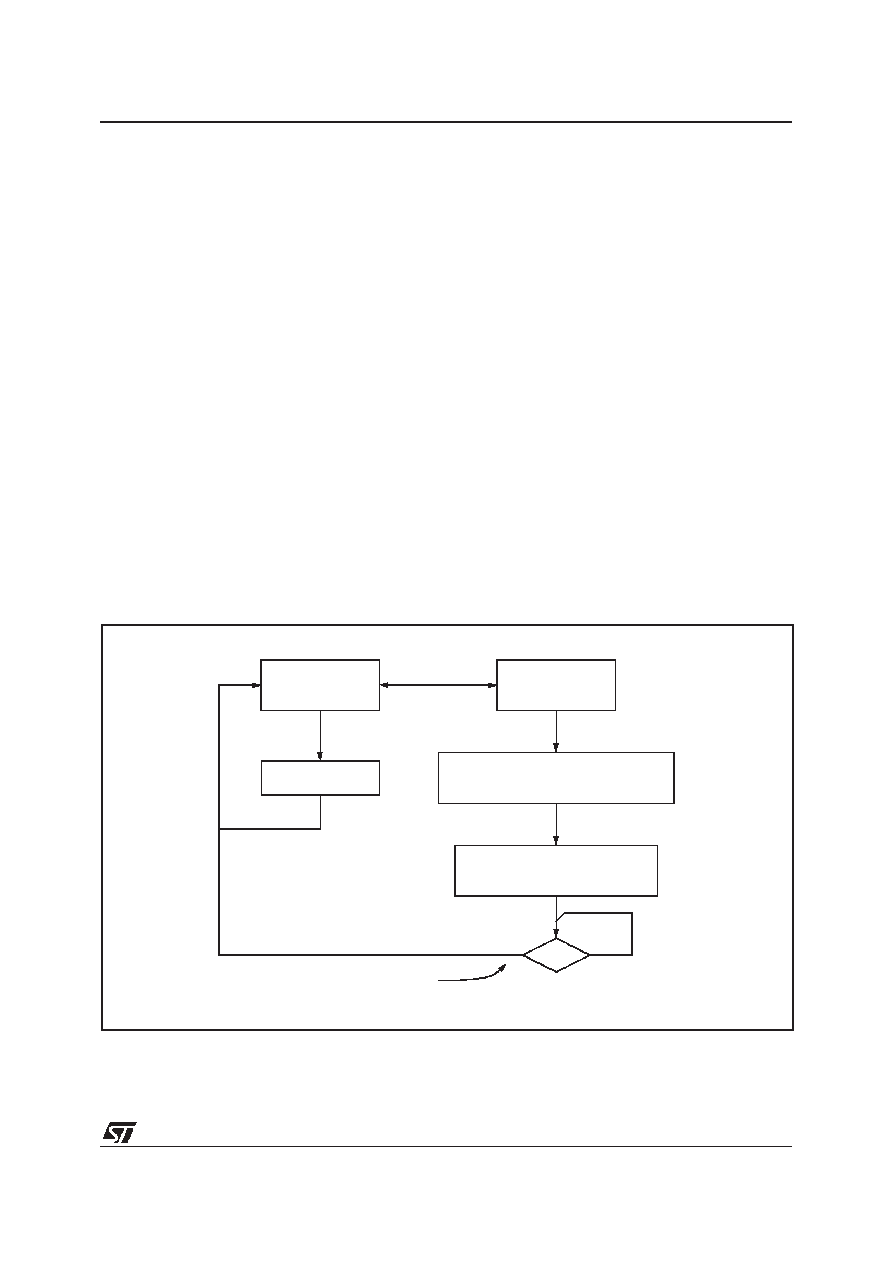

3.3 MEMORY ACCESS

The Data EEPROM memory read/write access

modes are controlled by the LAT bit of the EEP-

ROM Control/Status register (EECSR). The flow-

chart in Figure 5 describes these different memory

access modes.

Read Operation (LAT=0)

The EEPROM can be read as a normal ROM loca-

tion when the LAT bit of the EECSR register is

cleared. In a read cycle, the byte to be accessed is

put on the data bus in less than 1 CPU clock cycle.

This means that reading data from EEPROM

takes the same time as reading data from

EPROM, but this memory cannot be used to exe-

cute machine code.

Write Operation (LAT=1)

To access the write mode, the LAT bit has to be

set by software (the PGM bit remains cleared).

When a write access to the EEPROM area occurs,

the value is latched inside the 16 data latches ac-

cording to its address.

When PGM bit is set by the software, all the previ-

ous bytes written in the data latches (up to 16) are

programmed in the EEPROM cells. The effective

high address (row) is determined by the last EEP-

ROM write sequence. To avoid wrong program-

ming, the user must take care that all the bytes

written between two programming sequences

have the same high address: only the four Least

Significant Bits of the address can change.

At the end of the programming cycle, the PGM and

LAT bits are cleared simultaneously, and an inter-

rupt is generated if the IE bit is set. The Data EEP-

ROM interrupt request is cleared by hardware

when the Data EEPROM interrupt vector is

fetched.

Note: Care should be taken during the program-

ming cycle. Writing to the same memory location

will over-program the memory (logical AND be-

tween the two write access data result) because

the data latches are only cleared at the end of the

programming cycle and by the falling edge of LAT

bit.

It is not possible to read the latched data.

This note is ilustrated by the Figure 6.

Figure 5. Data EEPROM Programming Flowchart

READ MODE

LAT=0

PGM=0

WRITE MODE

LAT=1

PGM=0

READ BYTES

IN EEPROM AREA

WRITE UP TO 16 BYTES

IN EEPROM AREA

(with the same 12 MSB of the address)

START PROGRAMMING CYCLE

LAT=1

PGM=1 (set by software)

LAT

INTERRUPT GENERATION

IF IE=1

0

1

CLEARED BY HARDWARE

相关PDF资料 |

PDF描述 |

|---|---|

| ST72T511R7T1 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72T631L4M1 | 8-BIT, OTPROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| SAB80C537-M | 8-BIT, 12 MHz, MICROCONTROLLER, PQFP100 |

| SAF-C504-2R40M | 8-BIT, MROM, 40 MHz, MICROCONTROLLER, PQFP44 |

| SAB-C517A-4R24M | 8-BIT, MROM, 24 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72561K4 | 制造商:STMicroelectronics 功能描述:LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,FLASH MEMORY, - Bulk |

| ST72589-EMU2 | 功能描述:仿真器/模拟器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 产品:System Trace Emulators 工具用于评估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST72611F1 | 制造商:STMicroelectronics 功能描述:LOW SPEED USB 8-BIT MCU WITH 3 ENDPOINTS,FLASH MEMORY, - Bulk |

| ST7263-EMU2 | 功能描述:仿真器/模拟器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 产品:System Trace Emulators 工具用于评估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

发布紧急采购,3分钟左右您将得到回复。