- 您现在的位置:买卖IC网 > PDF目录98145 > ST72621J2B1 (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP20 PDF资料下载

参数资料

| 型号: | ST72621J2B1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP20 |

| 封装: | 0.300 INCH, PLASTIC, DIP-20 |

| 文件页数: | 120/136页 |

| 文件大小: | 2475K |

| 代理商: | ST72621J2B1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页当前第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页

ST7262

84/136

USB INTERFACE (Cont’d)

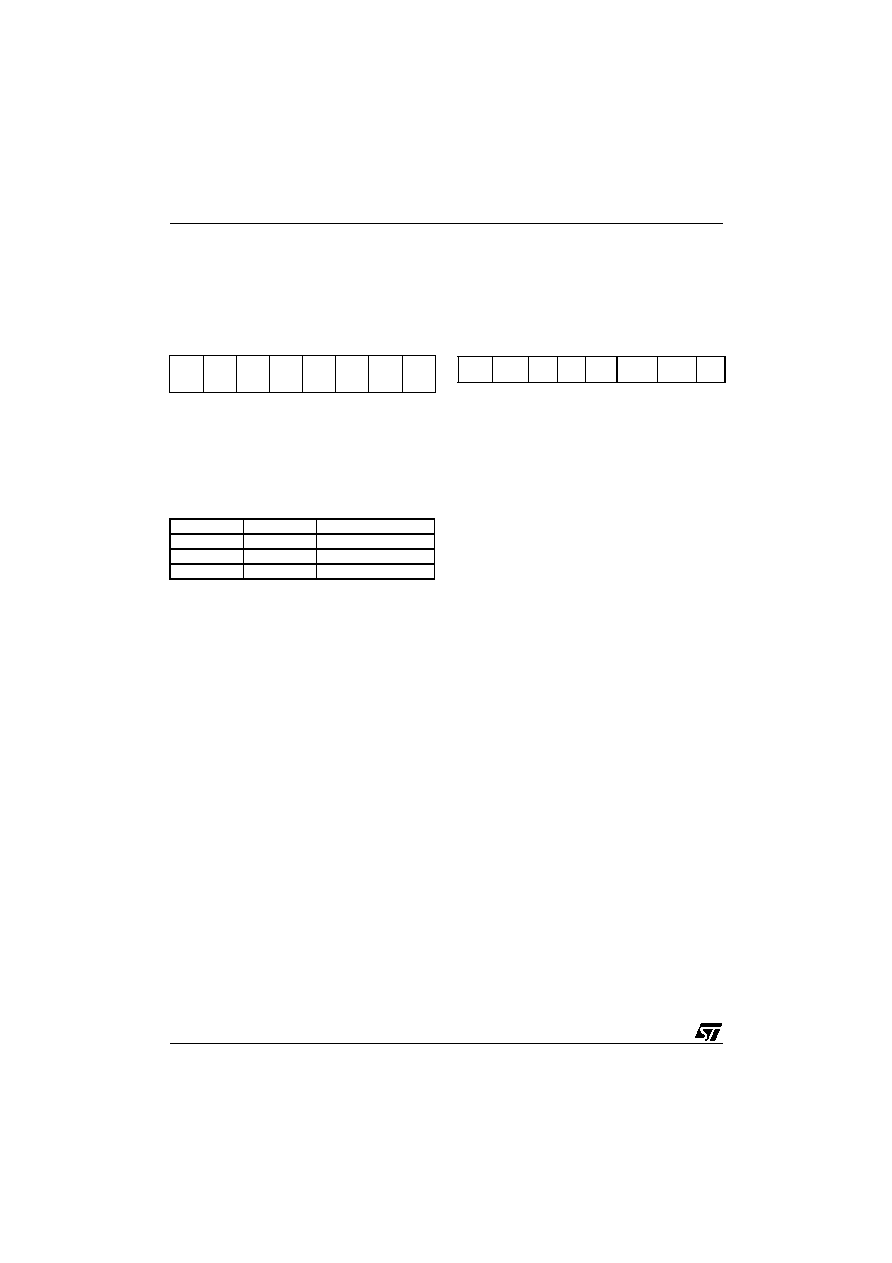

PID REGISTER (PIDR)

Read only

Reset Value: xx00 0000 (x0h)

Bits 7:6 = TP[3:2] Token PID bits 3 & 2.

USB token PIDs are encoded in four bits. TP[3:2]

correspond to the variable token PID bits 3 & 2.

Note: PID bits 1 & 0 have a fixed value of 01.

When a CTR interrupt occurs (see register ISTR)

the software should read the TP3 and TP2 bits to

retrieve the PID name of the token received.

The USB standard defines TP bits as:

Bits 5:3 Reserved. Forced by hardware to 0.

Bit 2 = RX_SEZ Received single-ended zero

This bit indicates the status of the RX_SEZ trans-

ceiver output.

0: No SE0 (single-ended zero) state

1: USB lines are in SE0 (single-ended zero) state

Bit 1 = RXD Received data

0: No K-state

1: USB lines are in K-state

This bit indicates the status of the RXD transceiver

output (differential receiver output).

Note: If the environment is noisy, the RX_SEZ and

RXD bits can be used to secure the application. By

interpreting the status, software can distinguish a

valid End Suspend event from a spurious wake-up

due to noise on the external USB line. A valid End

Suspend is followed by a Resume or Reset se-

quence. A Resume is indicated by RXD=1, a Re-

set is indicated by RX_SEZ=1.

Bit 0 = Reserved. Forced by hardware to 0.

INTERRUPT STATUS REGISTER (ISTR)

Read / Write

Reset Value: 0000 0000 (00h)

When an interrupt occurs these bits are set by

hardware. Software must read them to determine

the interrupt type and clear them after servicing.

Note: These bits cannot be set by software.

Bit 7 = SUSP Suspend mode request.

This bit is set by hardware when a constant idle

state is present on the bus line for more than 3 ms,

indicating a suspend mode request from the USB

bus. The suspend request check is active immedi-

ately after each USB reset event and its disabled

by hardware when suspend mode is forced

(FSUSP bit of CTLR register) until the end of

resume sequence.

Bit 6 = DOVR DMA over/underrun.

This bit is set by hardware if the ST7 processor

can’t answer a DMA request in time.

0: No over/underrun detected

1: Over/underrun detected

Bit 5 = CTR Correct Transfer. This bit is set by

hardware when a correct transfer operation is per-

formed. The type of transfer can be determined by

looking at bits TP3-TP2 in register PIDR. The End-

point on which the transfer was made is identified

by bits EP1-EP0 in register IDR.

0: No Correct Transfer detected

1: Correct Transfer detected

Note: A transfer where the device sent a NAK or

STALL handshake is considered not correct (the

host only sends ACK handshakes). A transfer is

considered correct if there are no errors in the PID

and CRC fields, if the DATA0/DATA1 PID is sent

as expected, if there were no data overruns, bit

stuffing or framing errors.

Bit 4 = ERR Error.

This bit is set by hardware whenever one of the er-

rors listed below has occurred:

0: No error detected

1: Timeout, CRC, bit stuffing or nonstandard

framing error detected

70

TP3

TP2

0

RX_

SEZ

RXD

0

TP3

TP2

PID Name

00

OUT

10

IN

11

SETUP

70

SUSP

DOVR

CTR

ERR

IOVR

ESUSP

RESET

SOF

相关PDF资料 |

PDF描述 |

|---|---|

| ST72621J2T1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO20 |

| ST72P621L4M1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDSO34 |

| ST72623F2M1L | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO34 |

| ST7263BK1B/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP32 |

| ST72652AR4T1/XXX | 8-BIT, MROM, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7263-EMU2 | 功能描述:仿真器/模拟器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 产品:System Trace Emulators 工具用于评估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

| ST7267C8T1L | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。