- 您现在的位置:买卖IC网 > PDF目录271213 > ST72621L4M1 (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO34 PDF资料下载

参数资料

| 型号: | ST72621L4M1 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDSO34 |

| 封装: | 0.300 INCH, LEAD FREE, SHRINK, PLASTIC, SOP-34 |

| 文件页数: | 127/139页 |

| 文件大小: | 1264K |

| 代理商: | ST72621L4M1 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页当前第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页

ST7262xxx

88/139

Doc ID 6996 Rev 5

USB INTERFACE (Cont’d)

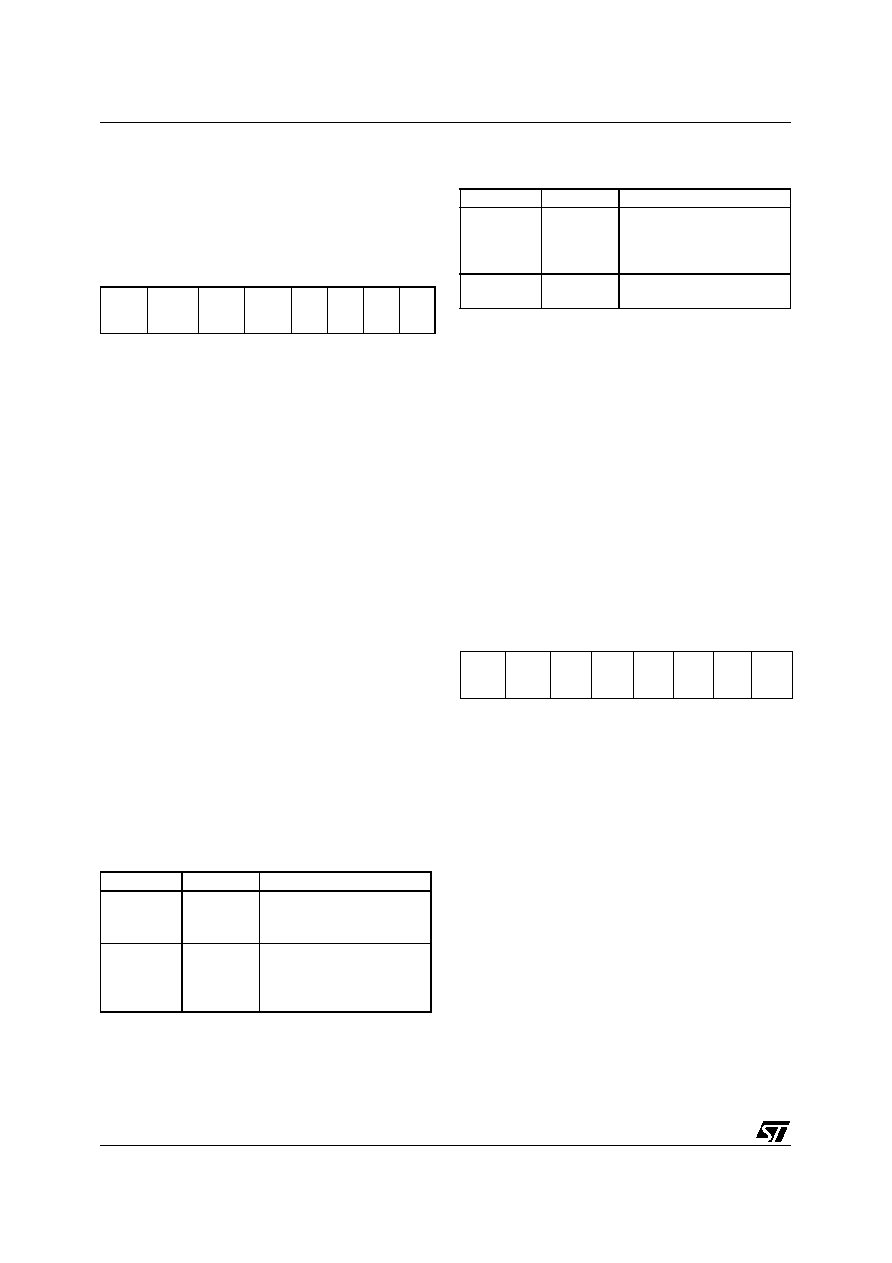

ENDPOINT n REGISTER B (EPnRB)

Read / Write

Reset Value: 0000 xxxx (0xh)

These registers (EP1RB and EP2RB) are used for

controlling data reception on Endpoints 1 and 2.

They are also reset by the USB bus reset.

Note: Endpoint 2 and the EP2RB register are not

available on some devices (see device feature list

and register map).

Bit 7 = CTRL Control.

This bit should be 0.

Note: If this bit is 1, the Endpoint is a control end-

point. (Endpoint 0 is always a control Endpoint, but

it is possible to have more than one control End-

point).

Bit 6 = DTOG_RX Data toggle, for reception trans-

fers.

It contains the expected value of the toggle bit

(0=DATA0, 1=DATA1) for the next data packet.

This bit is cleared by hardware in the first stage

(Setup Stage) of a control transfer (SETUP trans-

actions start always with DATA0 PID). The receiv-

er toggles DTOG_RX only if it receives a correct

data packet and the packet’s data PID matches

the receiver sequence bit.

Bits 5:4 = STAT_RX [1:0] Status bits, for reception

transfers.

These bits contain the information about the end-

point status, which are listed below:

These bits are written by software. Hardware sets

the STAT_RX bits to NAK when a correct transfer

has occurred (CTR=1) related to an OUT or SET-

UP transaction addressed to this endpoint, so the

software has the time to elaborate the received

data before acknowledging a new transaction.

Bits 3:0 = EA[3:0] Endpoint address.

Software must write in this field the 4-bit address

used to identify the transactions directed to this

endpoint. Usually EP1RB contains “0001” and

EP2RB contains “0010”.

ENDPOINT 0 REGISTER B (EP0RB)

Read / Write

Reset Value: 1000 0000 (80h)

This register is used for controlling data reception

on Endpoint 0. It is also reset by the USB bus re-

set.

Bit 7 = Forced by hardware to 1.

Bits 6:4 = Refer to the EPnRB register for a de-

scription of these bits.

Bits 3:0 = Forced by hardware to 0.

70

CTRL

DTOG

_RX

STAT

_RX1

STAT

_RX0

EA3

EA2

EA1

EA0

STAT_RX1

STAT_RX0 Meaning

00

DISABLED: reception

transfers cannot be exe-

cuted.

01

STALL: the endpoint is

stalled and all reception

requests

result

in

a

STALL handshake.

10

NAK: the endpoint is na-

ked and all reception re-

quests result in a NAK

handshake.

11

VALID: this endpoint is

enabled for reception.

70

1

DTOG

RX

STAT

RX1

STAT

RX0

00

0

STAT_RX1

STAT_RX0 Meaning

相关PDF资料 |

PDF描述 |

|---|---|

| ST72F521R7T6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 |

| SPAK5307CFT66 | 32-BIT, 66 MHz, RISC PROCESSOR, PQFP208 |

| SAF-C505CA-4R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

| S1C60N01D | 4-BIT, MROM, 0.08 MHz, MICROCONTROLLER, UUC46 |

| S3S12P128J0CQKR | 16-BIT, MROM, 1.05 MHz, MICROCONTROLLER, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST7263-EMU2 | 功能描述:仿真器/模拟器 ST7 Emulator Board RoHS:否 制造商:Blackhawk 产品:System Trace Emulators 工具用于评估:C6000, C5000, C2000, OMAP, DAVINCI, SITARA, TMS470, TMS570, ARM 7/9, ARM Cortex A8/R4/M3 用于:XDS560v2 |

| ST7265X-EVAL/MS | 制造商:STMicroelectronics 功能描述:ST6 EVAL BD - Bulk |

| ST7265X-EVAL/PFD | 制造商:STMicroelectronics 功能描述:USB FLASH EVAL - Bulk |

| ST7266 | 制造商:6940 功能描述:ST7266 |

| ST7267C8T1L | 制造商:STMicroelectronics 功能描述: |

发布紧急采购,3分钟左右您将得到回复。