- 您现在的位置:买卖IC网 > PDF目录69354 > ST72C314J4B1XXX (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP42 PDF资料下载

参数资料

| 型号: | ST72C314J4B1XXX |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP42 |

| 封装: | 0.600 INCH, PLASTIC, SDIP-42 |

| 文件页数: | 80/153页 |

| 文件大小: | 2235K |

| 代理商: | ST72C314J4B1XXX |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页当前第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页

ST72334J/N, ST72314J/N, ST72124J

32/153

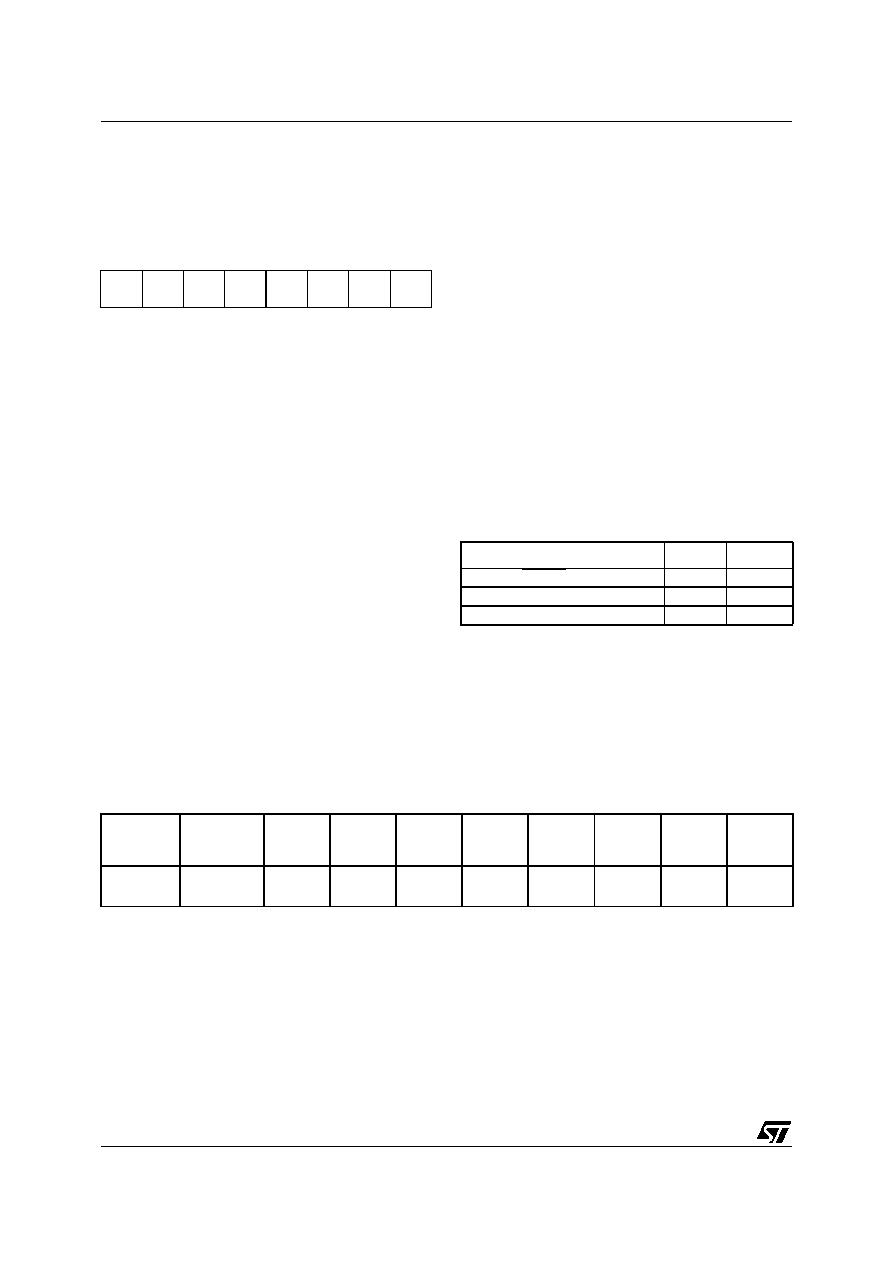

9.5 SUPPLY, RESET AND CLOCK REGISTER DESCRIPTION

Read /Write

Reset Value: 000x 000x (xxh)

Bit 7:5 = Reserved, always read as 0.

Bit 4 = LVDRF

LVD reset flag

This bit indicates that the last RESET was gener-

ated by the LVD block. It is set by hardware (LVD

reset) and cleared by software (writing zero). See

WDGRF flag description for more details. When

the LVD is disabled by option byte, the LVDRF bit

value is undefined.

Bit 3 = Reserved, always read as 0.

Bit 2 = CSSIE

Clock security syst

.

interrupt enable

This bit enables the interrupt when a disturbance

is detected by the clock security system (CSSD bit

set). It is set and cleared by software.

0: Clock security system interrupt disabled

1: Clock security system interrupt enabled

for more details on the CSS interrupt vector. When

the CSS is disabled by option byte, the CSSIE bit

has no effect.

Bit 1 = CSSD

Clock security system detection

This bit indicates that the safe oscillator of the

clock security system block has been selected by

hardware due to a disturbance on the main clock

signal (fOSC). It is set by hardware and cleared by

reading the CRSR register when the original oscil-

lator recovers.

0: Safe oscillator is not active

1: Safe oscillator has been activated

When the CSS is disabled by option byte, the

CSSD bit value is forced to 0.

Bit 0 = WDGRF

Watchdog reset flag

This bit indicates that the last RESET was gener-

ated by the watchdog peripheral. It is set by hard-

ware (Watchdog RESET) and cleared by software

(writing zero) or an LVD RESET (to ensure a sta-

ble cleared state of the WDGRF flag when the

CPU starts).

Combined with the LVDRF flag information, the

flag description is given by the following table.

Application notes

The LVDRF flag is not cleared when another RE-

SET type occurs (external or watchdog), the

LVDRF flag remains set to keep trace of the origi-

nal failure.

In this case, a watchdog reset can be detected by

software while an external reset can not.

Table 4. Clock, Reset and Supply Register Map and Reset Values

70

000

LVD

RF

0

CSS

IE

CSS

D

WDG

RF

RESET Sources

LVDRF

WDGRF

External RESET pin

0

Watchdog

0

1

LVD

1

X

Address

(Hex.)

Register

Label

76

54321

0

002Bh

CRSR

Reset Value

0

LVDRF

x0

CFIE

0

CSSD

0

WDGRF

x

相关PDF资料 |

PDF描述 |

|---|---|

| ST72C314J4T1XXX | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72C334J4T1XXX | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72C334N4B3XXX | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP56 |

| ST72321BAR6T7/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

| ST72321BR6T7/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ST72C314J4B6 | 功能描述:8位微控制器 -MCU Flash 16K SPI/SCI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72C314J4T1 | 制造商:STMicroelectronics 功能描述:ST72FLASH 8K - Bulk |

| ST72C314J4T6 | 功能描述:8位微控制器 -MCU Flash 16K SPI/SCI RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| ST72C314J4T6 PROGRAMMED | 制造商:STMicroelectronics 功能描述:MCU 8-bit ST7 CISC 16KB Flash 3.3V/5V 44-Pin TQFP Tray |

| ST72C314J4T6E | 制造商:STMicroelectronics 功能描述:16K TQFP44 LEADFREE - Trays |

发布紧急采购,3分钟左右您将得到回复。