- 您现在的位置:买卖IC网 > PDF目录97149 > SY100S331JYTR (MICREL INC) 100S SERIES, TRIPLE POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PQCC28 PDF资料下载

参数资料

| 型号: | SY100S331JYTR |

| 厂商: | MICREL INC |

| 元件分类: | 锁存器 |

| 英文描述: | 100S SERIES, TRIPLE POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PQCC28 |

| 封装: | LEAD FREE, PLASTIC, LCC-28 |

| 文件页数: | 1/6页 |

| 文件大小: | 399K |

| 代理商: | SY100S331JYTR |

1

SY100S331

Micrel, Inc.

M9999-060910

hbwhelp@micrel.com or (408) 955-1690

TRIPLE D

FLIP-FLOP

SY100S331

■ Max.togglefrequencyof800MHz

■ Differentialoutputs

■ IEEmin.of–80mA

■ Industrystandard100KECLlevels

■ Extendedsupplyvoltageoption:

VEE=–4.2Vto–5.5V

■ Voltageandtemperaturecompensationforimproved

noiseimmunity

■ Internal75kinputpull-downresistors

■ 150%fasterthanFairchild

■ 40%lowerpowerthanFairchild

■ FunctionandpinoutcompatiblewithFairchildF100K

■ Availablein28-pinPLCCpackage

FEATURES

DESCRIPTION

TheSY100S331offersthreeD-type,edge-triggeredmaster/

slave flip-flops with true and complement outputs, designed

for use in high-performance ECL systems. Each flip-flop is

controlled by a common clock (CPc), as well as its own clock

pulse (CPn). The resultant clock signal controlling the flip-flop

is the logical OR operation of these two clock signals. Data

entersthemasterwhenbothCPc andCPn areLOWandenters

the slave on the rising edge of either CPc or CPn (or both).

Additional control signals include Master Set (MS) and

Master Reset (MR) inputs. Each flip-flop also has its own

Direct Set (SDn) and Direct Clear (CDn) signals. The MR, MS,

SDn and DCn signals override the clock signals. The inputs

on this device have 75k pull-down resistors.

Rev.: I

Amendment: /0

Issue Date: June 2010

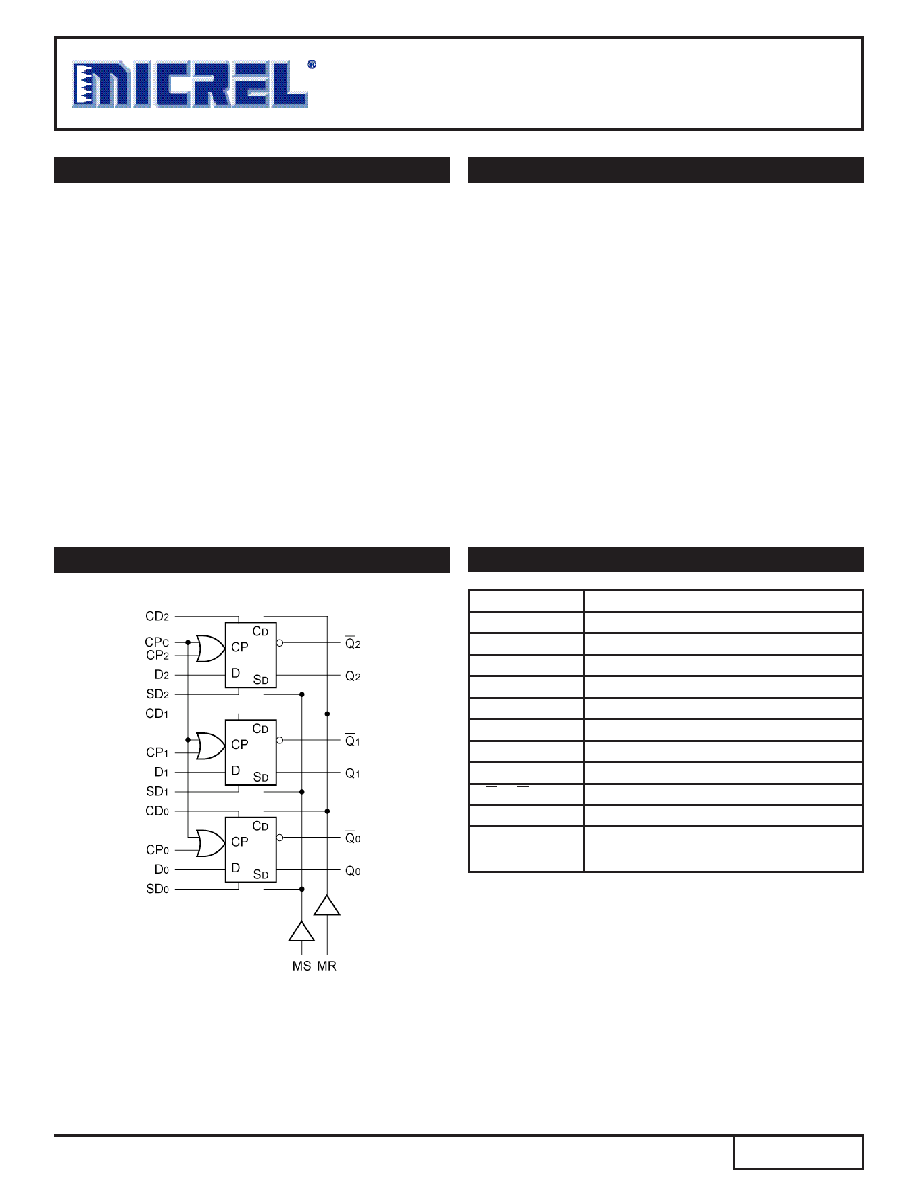

BLOCKDIAGRAM

Pin

Function

CP0 – CP2

Individual Clock Inputs

CPc

Common Clock Input

D0 – D2

Data Inputs

CD0 – CD2

Individual Direct Clear Inputs

SDn

Individual Direct Set Inputs

MR

Master Reset Input

MS

Master Set Input

Q0 – Q2

Data Outputs

Q0 – Q2

Complementary Data Outputs

VEES

VEE Substrate

VCCA

VCCO for ECL Outputs

PINNAMES

相关PDF资料 |

PDF描述 |

|---|---|

| SY100S351JY | 100S SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PQCC28 |

| SY100S360DC | 100S SERIES, 9-BIT PARITY GENERATOR/CHECKER, TRUE OUTPUT, CDIP24 |

| SY100S366DC | 100S SERIES, 9-BIT MAGNITUDE COMPARATOR, CDIP24 |

| SY100S370JC | 100S SERIES, OTHER DECODER/DRIVER, TRUE OUTPUT, PQCC28 |

| SY100S371JC | 100S SERIES, TRIPLE 4 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY100S331JZ | 功能描述:触发器 Triple D Flip-Flop (Lead Free) RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| SY100S331JZ TR | 功能描述:触发器 Triple D Flip-Flop (Lead Free) RoHS:否 制造商:Texas Instruments 电路数量:2 逻辑系列:SN74 逻辑类型:D-Type Flip-Flop 极性:Inverting, Non-Inverting 输入类型:CMOS 输出类型: 传播延迟时间:4.4 ns 高电平输出电流:- 16 mA 低电平输出电流:16 mA 电源电压-最大:5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:X2SON-8 封装:Reel |

| SY100S336AFC | 功能描述:IC COUNTER/SHIFT REG 24-CERPAC+G RoHS:否 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:100S 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| SY100S336AJC | 功能描述:IC COUNTER/SHIFT REG 28-PLCC RoHS:否 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:100S 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

| SY100S336FC | 功能描述:IC COUNTER/SHIFT REG 24-CERPACK RoHS:否 类别:集成电路 (IC) >> 逻辑 - 专用逻辑 系列:100S 产品变化通告:Product Discontinuation 25/Apr/2012 标准包装:1,500 系列:74SSTV 逻辑类型:DDR 的寄存缓冲器 电源电压:2.3 V ~ 2.7 V 位数:14 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:48-TFSOP(0.240",6.10mm 宽) 供应商设备封装:48-TSSOP 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。