参数资料

| 型号: | SY89229UMG |

| 厂商: | Micrel Inc |

| 文件页数: | 10/16页 |

| 文件大小: | 0K |

| 描述: | IC CLK DIVIDER /3/5 LVDS 16-MLF |

| 标准包装: | 100 |

| 系列: | Precision Edge® |

| 类型: | 时钟除法器 |

| PLL: | 无 |

| 输入: | CML,LVDS,PECL |

| 输出: | LVDS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 1GHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.375 V ~ 2.625 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 16-VFQFN 裸露焊盘,16-MLF? |

| 供应商设备封装: | 16-MLF?(3x3) |

| 包装: | 管件 |

| 产品目录页面: | 1083 (CN2011-ZH PDF) |

| 其它名称: | 576-1651-5 |

Micrel, Inc.

SY89229U

August 2007

M9999-080707-A

hbwhelp@micrel.com or (408) 955-1690

3

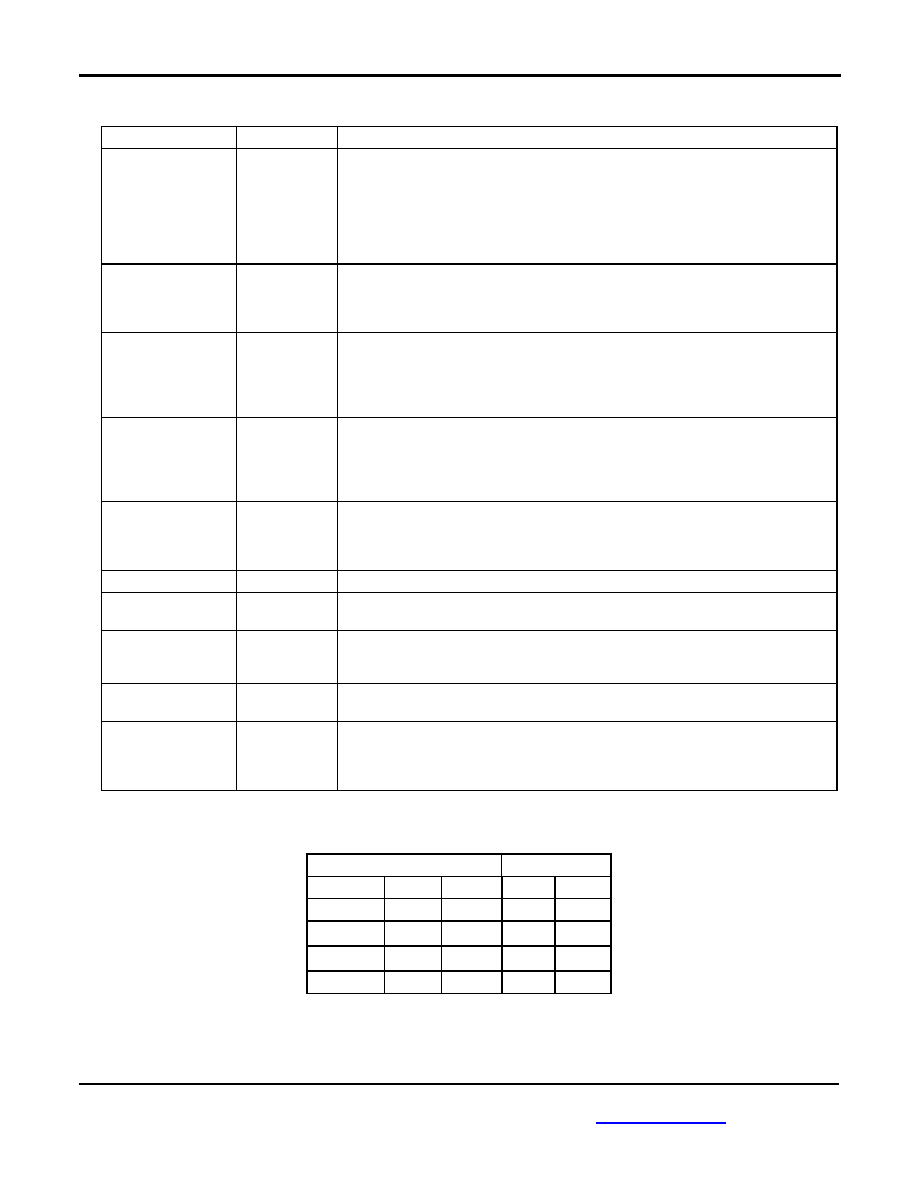

Pin Description

Pin Number

Pin Name

Pin Function

1, 4

IN, /IN

Differential Input: This input pair is the differential signal input to the device,

which accepts AC- or DC-coupled signal as small as 100mV. The input internally

terminates to a VT pin through 50

and has level shifting resistors of 3.72 k to

VCC. This allows a wide input voltage range from VCC to GND. See Figure 3,

Simplified Differential Input Stage for details. Note that this input will default to a

valid (either HIGH or LOW) state if left open. See “Input Interface Applications”

subsection.

2

VT

Input Termination Center-Tap: Each side of the differential input pair terminates

to the VT pin. The VT pin provides a center-tap for the input (IN, /IN) to a

termination network for maximum interface flexibility. See “Input Interface

Applications” subsection for more details.

3

VREF-AC

Reference Voltage: This output biases to VCC–1.2V. It is used for AC-coupling

inputs IN and /IN. Connect VREF-AC directly to the VT pin. Bypass with 0.01F

low ESR capacitor to VCC. Due to limited drive capability, the VREF-AC pin is

only intended to drive its respective VT pin. Maximum sink/source current is

±0.5mA. See “Input Interface Applications” subsection.

5

EN

Single-ended Input: This TTL/CMOS-compatible input disables and enables the

output. It is internally connected to a 25k

pull-up resistor and will default to a

logic HIGH state if left open. When disabled, Q goes LOW and /Q goes HIGH.

EN being synchronous, outputs will be enabled/disabled after a rising and a

falling edge of the input clock. VTH = VCC/2.

6

/MR

Single-ended Input: This TTL/CMOS-compatible input, when pulled LOW,

asynchronously sets Q output LOW and /Q output HIGH. Note that this input is

internally connected to a 25k

pull-up resistor and will default to logic HIGH

state if left open. VTH = VCC/2.

7

NC

No Connect

8, 13

VCC

Positive Power Supply: Bypass with 0.1F in parallel with 0.01F low ESR

capacitors as close to the VCC pins as possible.

12, 9

Q, /Q

Differential Output: The output swing is typically 325mV. The output must be

terminated with 100

across the pair (Q, /Q). See the “Truth Table” below for the

logic function.

10, 11, 14,15

GND,

Exposed Pad

Ground: Ground and exposed pad must be connected to a ground plane that is

the same potential as the ground pins.

16

DIV_SEL

Single-ended Input: This TTL/CMOS-compatible input selects divide-by-3 when

pulled LOW and divide-by-5 when pulled HIGH. Note that this input is internally

connected to a 25k

pull-up resistor and will default to logic HIGH state if left

open. VTH = VCC/2.

Truth Table

Inputs

Outputs

DIV_SEL

EN

/MR

Q

/Q

X

0

1

0

1

÷3

1

÷5

X

0

1

0

1

相关PDF资料 |

PDF描述 |

|---|---|

| VE-27L-MW-S | CONVERTER MOD DC/DC 28V 100W |

| VE-BWB-MV-S | CONVERTER MOD DC/DC 95V 150W |

| VI-2T2-MY-F3 | CONVERTER MOD DC/DC 15V 50W |

| ADF4107BRU-REEL | IC PLL FREQ SYNTHESIZER 16-TSSOP |

| VI-2TX-IV | CONVERTER MOD DC/DC 5.2V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY89229UMG TR | 功能描述:时钟驱动器及分配 Divide-by-3 and 5 LVDS Clock Divider with Internal Termination and FSI (1GHz) RoHS:否 制造商:Micrel 乘法/除法因子:1:4 输出类型:Differential 最大输出频率:4.2 GHz 电源电压-最大: 电源电压-最小:5 V 最大工作温度:+ 85 C 封装 / 箱体:SOIC-8 封装:Reel |

| SY89229UMGTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:1GHz Precision, LVDS ÷3, ÷5 Clock Divider with Fail Safe Input and Internal Termination |

| SY89230U | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:1GHz Precision, LVPECL ±3, ±5 Clock Divider with Fail-Safe Input and Internal Termination |

| SY89230U_10 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.2GHz Precision, LVPECL ÷3, ÷5 Clock Divider |

| SY89230U-EVAL | 制造商:Micrel Inc 功能描述:DIVIDE-BY-3 AND 5 LVPECL CLOCK |

发布紧急采购,3分钟左右您将得到回复。