- 您现在的位置:买卖IC网 > PDF目录98150 > SY89531LHZ (MICREL INC) 622.08 MHz, OTHER CLOCK GENERATOR, PQFP64 PDF资料下载

参数资料

| 型号: | SY89531LHZ |

| 厂商: | MICREL INC |

| 元件分类: | 时钟产生/分配 |

| 英文描述: | 622.08 MHz, OTHER CLOCK GENERATOR, PQFP64 |

| 封装: | LEAD FREE, TQFP-64 |

| 文件页数: | 13/16页 |

| 文件大小: | 105K |

| 代理商: | SY89531LHZ |

6

Precision Edge

SY89531L

Micrel, Inc.

M9999-010808

hbwhelp@micrel.com or (408) 955-1690

V

CC_LOGIC = VCCA = VCCOA/C = +3.3V ±10%, VCCOB = +1.8V ±10%

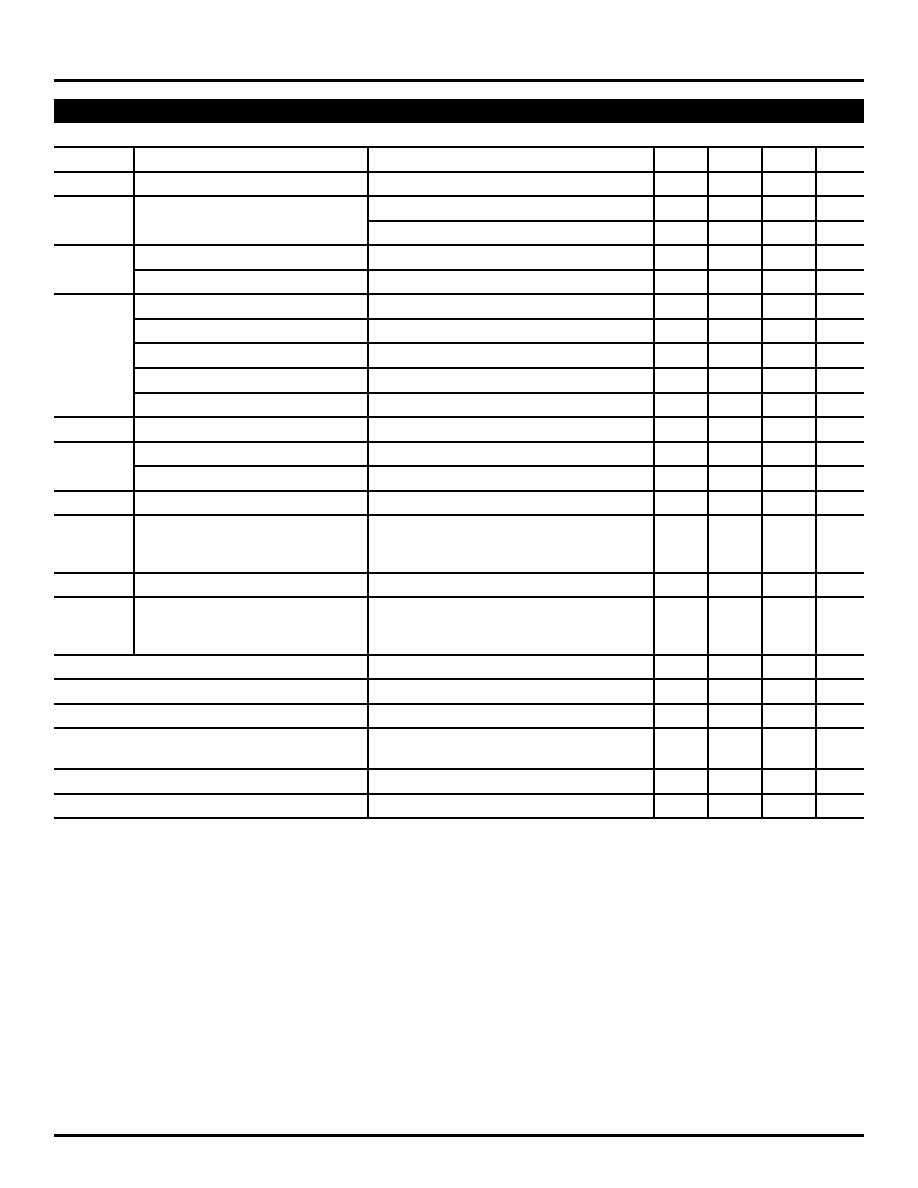

Symbol

Parameter

Condition

Min

Typ

Max

Units

fIN

Xtal Input Frequency Range

Note 8

14

—

18

MHz

fOUT

Output Frequency Range

w/Internal VCO

33.33

—

500

MHz

w/External VCO

——

622.08

MHz

tVCO

Internal VCO Frequency Range

600

—

1000

MHz

External VCO Frequency

——

1250

MHz

tskew

Within Device Skew

——

50

ps

Note 9

Within-Bank PECL

——

50

ps

Within-Bank HSTL

——

75

ps

Between Banks

——

150

ps

Part-to-Part Skew

Note 10

——

200

ps

tLOCK

Maximum PLL Lock Time

——

10

ms

tJITTER

Cycle-to-Cycle Jitter

(Pk-to-Pk)

Note 11

—

25

—

ps

Period Jitter

(RMS)

Note 12

——

50

ps

tpw (min)

Minimum Pulse Width

50

——

ns

Target PLL Loop Bandwidth

Feedback Divider Ratio: 72

Note 13

—

1.0

—

MHz

Feedback Divider Ratio: 34

Note 13

—

2.0

—

MHz

tDC

fOUT Duty Cycle

45

50

55

%

tr, tf

Output Rise/Fall Time

(20% to 80%)LVPECL_Out

—

250

450

ps

HSTL_Out

100

—

450

ps

tOUTPUT_RESET

Note 14

——

10

ns

tHOLD_FSEL

5

——

ns

tSETUP_FSEL

5

——

ns

tOUTPUT_SYNC

1

——

VCO

clock cycle

FSEL-to-Valid Output Transition Time

——

1

s

tSETUP_OUT_SYNC

500

——

ps

Note 8.

Fundamental mode crystal.

Note 9.

The within-device skew is defined as the worst case difference between any two similar delay paths within a single device operating at the

same voltage and temperature.

Note 10. The part-to-part skew is defined as the absolute worst case difference between any two delay paths on any two devices operating at the same

voltage and temperature.

Note 11. Cycle-to-cycle jitter definition: The variation in period between adjacent cycles over a random sample of adjacent cycle pairs. T

JITTER_CC =Tn–

T

n+1 where T is the time between rising edges of the output signal.

Note 12. Period Jitter definition: For a specified amount of time (i.e., 1ms), there are N periods of a signal, and T

n is defined as the average period of

that signal. Period jitter is defined as the variation in the period of the output signal for corresponding edges relative to T

n.

Note 13. Using recommended loop filter components. See

“Functional Description, External Loop Filter Considerations.”

Note 14. See

“Timing Diagrams.”

AC ELECTRICAL CHARACTERISTICS

相关PDF资料 |

PDF描述 |

|---|---|

| SY89534LHZ | 89534 SERIES, PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

| SY89534LHZTR | 89534 SERIES, PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

| SY89536LHZ | 89536 SERIES, PLL BASED CLOCK DRIVER, 13 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

| SY89537LMHTR | 756 MHz, OTHER CLOCK GENERATOR, QCC44 |

| SY89827LHG | 89827 SERIES, LOW SKEW CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY89531LHZ TR | 功能描述:时钟合成器/抖动清除器 3.3V Programmable HSTL/LVPECL Synthesizer (Green) RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| SY89531LHZTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, PRECISION, 33MHz to 500MHz PROGRAMMABLE LVPECL AND |

| SY89532L | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, PRECISION, 33MHz to 500MHz PROGRAMMABLE LVPECL AND HSTL BUS CLOCK SYNTHESIZER |

| SY89532L_08 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, PRECISION, 33MHz to 500MHz PROGRAMMABLE LVPECL AND LVDS BUS CLOCK SYNTHESIZER |

| SY89532LHC | 功能描述:IC SYNTHESIZR LVPECL/LVDS 64TQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:Precision Edge® 产品变化通告:Product Discontinuation 04/May/2011 标准包装:96 系列:- 类型:时钟倍频器,零延迟缓冲器 PLL:带旁路 输入:LVTTL 输出:LVTTL 电路数:1 比率 - 输入:输出:1:8 差分 - 输入:输出:无/无 频率 - 最大:133.3MHz 除法器/乘法器:是/无 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:管件 其它名称:23S08-5HPGG |

发布紧急采购,3分钟左右您将得到回复。