参数资料

| 型号: | SY89809LTH TR |

| 厂商: | Micrel Inc |

| 文件页数: | 3/8页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK BUFFER MUX 2:9 32-TQFP |

| 标准包装: | 1,000 |

| 系列: | Precision Edge® |

| 类型: | 扇出缓冲器(分配),多路复用器 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:9 |

| 差分 - 输入:输出: | 是/是 |

| 输入: | HSTL,LVPECL |

| 输出: | HSTL |

| 频率 - 最大: | 500MHz |

| 电源电压: | 3 V ~ 3.6 V |

| 工作温度: | 0°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-TQFP |

| 供应商设备封装: | 32-TQFP |

| 包装: | 带卷 (TR) |

| 其它名称: | SY89809LTHTR SY89809LTHTR-ND |

Micrel, Inc.

SY89809L

December 2009

3

M9999-121409-D

hbwhelp@micrel.com or (408) 955-1690

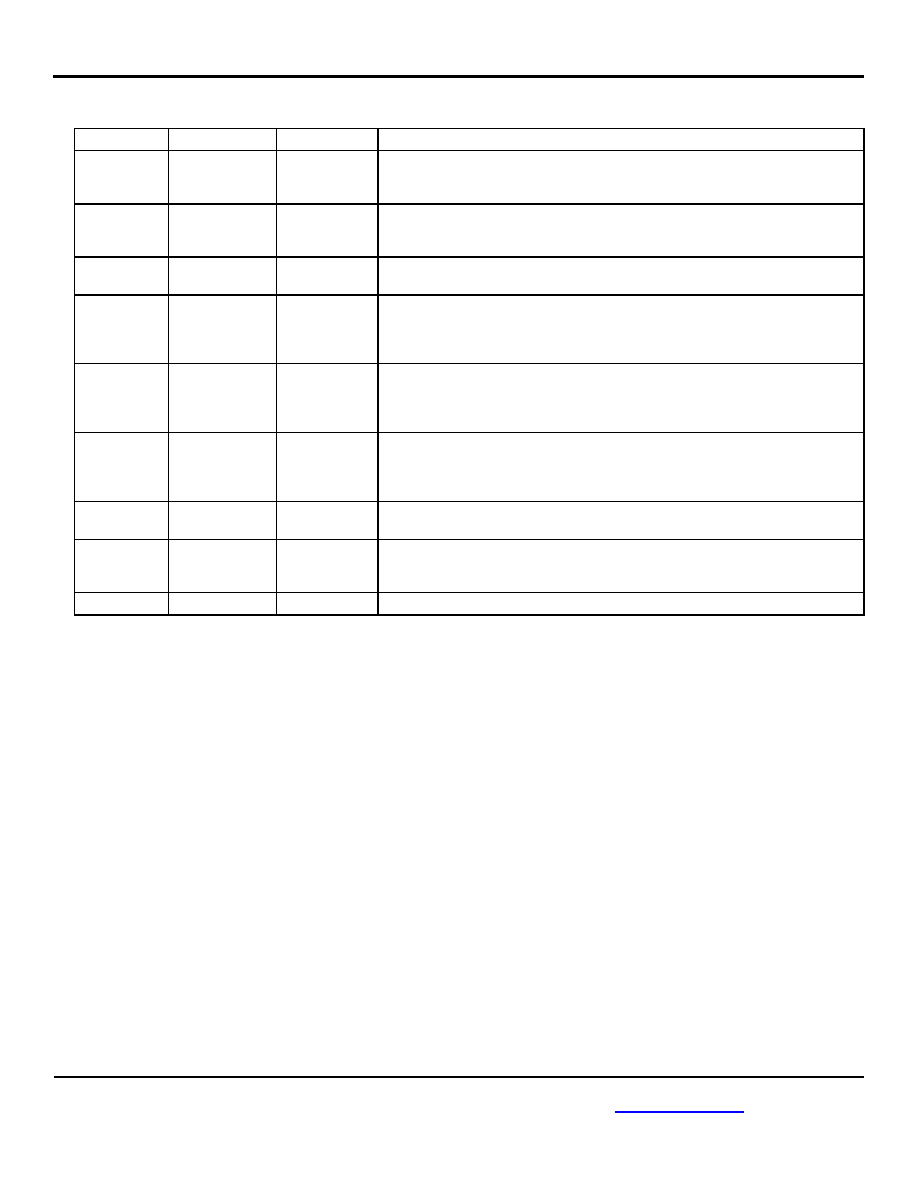

Pin Description

Pin Number

Pin Name

Type

Pin Function

2, 3

HSTL_CLK,

/HSTL_CLK

HSTL Input

Differential input: This HSTL input can be selected by CLK_SEL. If it is not

used, it can be left floating. This produces a LOW at the output. If driven by an

HSTL driver, an external 50 to ground termination is required at the input.

5, 6

LVPECL_CLK,

/LVPECL_CLK

LVPECL

Input

Differential input: This LVPECL input can be selected by CLK_SEL. If it is not

used, it can be left floating. This produces a LOW at the output (internal 75k

pull-downs).

4

CLK_SEL

LVTTL Input

Selected HSTL_CLK input when LOW and LVPECL_CLK output when HIGH.

11k pull-up.

8

OE

LVTTL Input

Single-ended input: This LVTTL input disables and enables the Q0-Q8 output

pairs. It is internally synchronized to prevent glitching of the Q0-Q8 output

pairs. It is internally connected to a 11k pull-up resistor and will default to a

logic HIGH state if left open.

31, 29, 27,

23, 21, 19,

15, 13, 11

Q0 – Q8

HSTL Output

Differential clock outputs from HSTL_CLK when CLK_SEL = LOW and

LVPECL outputs when CLK_SEL = HIGH. HSTL outputs must be terminated

with 50 to GND. Q0-Q8 outputs are static LOW when OE = LOW. Unused

output pairs may be left floating.

30, 28, 26,

22, 20, 18,

14, 12, 10

/Q0 – /Q8

HSTL Output

Differential clock outputs from HSTL_CLK when CLK_SEL = LOW and

LVPECL outputs when CLK_SEL = HIGH. HSTL outputs must be terminated

with 50 to GND. /Q0-/Q8 outputs are static HIGH when OE = LOW. Unused

output pairs may be left floating.

1

VCCI

VCC Core

Power

Core VCC connected to 3.3V supply. Bypass with 0.1F in parallel with 0.01F

low ESR capacitors as close to VCCI pin as possible.

9, 16, 17,

24, 25, 32

VCCO

VCC Output

Power

Output Buffer VCC connected to 1.8V supply. Bypass with 0.1F in parallel

with 0.01F low ESR capacitors as close to VCCO pins as possible. All VCCO

pins should be connected together on the PCB.

7

GND

Ground

Ground.

相关PDF资料 |

PDF描述 |

|---|---|

| VE-B6H-IU-B1 | CONVERTER MOD DC/DC 52V 200W |

| SY89808LTG TR | IC CLK BUF MUX TRNSLA 2:9 32TQFP |

| SY10H842ZH TR | IC CLK BUFFER 1:4 160MHZ 16-SOIC |

| AD5433YRUZ-REEL | IC DAC 10BIT MULTIPLYING 20TSSOP |

| SY10H842LZH TR | IC CLK BUFFER 1:4 160MHZ 16-SOIC |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SY898225UH | 制造商:Synergy 功能描述: |

| SY89823L | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, 500MHz 1:22 DIFFERENTIAL HSTL (1.5V) FANOUT BUFFER/TRANSLATOR |

| SY89823L_08 | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, 500MHz 1:22 DIFFERENTIAL HSTL (1.5V) FANOUT BUFFER/TRANSLATOR |

| SY89823LHC | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, 500MHz 1:22 DIFFERENTIAL HSTL (1.5V) FANOUT BUFFER/TRANSLATOR |

| SY89823LHCTR | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:3.3V, 500MHz 1:22 DIFFERENTIAL HSTL (1.5V) FANOUT BUFFER/TRANSLATOR |

发布紧急采购,3分钟左右您将得到回复。