- 您现在的位置:买卖IC网 > PDF目录98158 > TAS3218IPZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF资料下载

参数资料

| 型号: | TAS3218IPZP |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 消费家电 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封装: | GREEN, PLASTIC, TQFP-100 |

| 文件页数: | 2/79页 |

| 文件大小: | 1263K |

| 代理商: | TAS3218IPZP |

第1页当前第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页

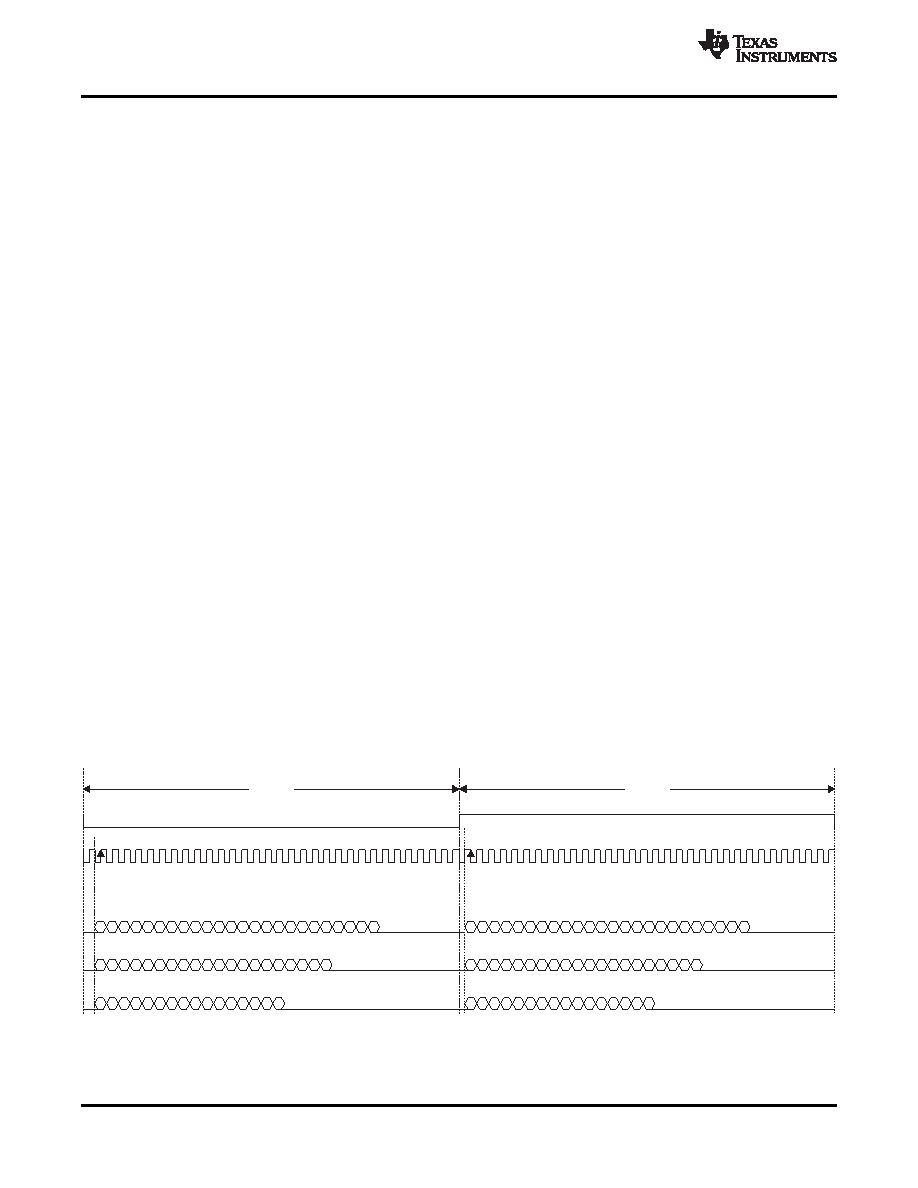

Digital Audio Data Formats

LRCLK (note reversed phase)

SCLK

2-Channel I S (Philips Format) Stereo Input

2

Left Channel

Right Channel

LSB

MSB

LSB

32 clks

24-Bit Mode

20-Bit Mode

16-Bit Mode

23 22 21 20 19 18 17 16 15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

23 22 21 20 19 18 17 16 15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

19 18 17 16 15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

19 18 17 16 15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

15 14 13

10

9

8

7

6

5

4

3

2

1

0

12 11

SLES235 – JULY 2008 ....................................................................................................................................................................................................... www.ti.com

MCLKOUT, SCLKOUT, and LRCLKOUT are passed through from the clock inputs MCLKIN, SCLKIN, and

LCLKIN.

MCLKIN 256 Fs is supplied externally

SCLKIN 64 Fs is supplied externally

LRCLKIN Fs is supplied externally

NOTE:

In slave mode all incoming serial audio data must be synchronous to an incoming

LRCLKIN of 32, 44.1 or 48 kHz. The TAS3218 does not support the use of an

external (i.e., 24 MHz) clock input through into XTALI

Serial data is input on pins SDIN1-3 on the TAS3218, allowing up to 6 channels of digital audio input. The

TAS3218 supports 16-, 20-, or 24-bit data in left, right, or I2S serial data format. By default, all TAS3218 serial

digital inputs are configured in the 24-bit I2S format. The serial data input format is configurable via the

SAP/Clock Settings Register.

Serial data is output on pins SDOUT1-2, allowing up to 4 channels of digital audio output. By default, the SDOUT

data format is 24-bit, I2S format at the same data rate as the input. The SDOUT1-2 output uses the SCLKOUT

and LRCLKOUT signals to provide synchronization. SDOUT2 is multiplexed with an SPDIF output.

NOTE:

To avoid audio artifacts, I2C commands to reconfigure the serial audio port (SAP)

should not be issued as standalone commands, rather should be accompanied by

mute and unmute commands.

The TAS3218 uses the SCLK as a reference for both input and output samples. The negative edge of SCLK is

used to output a new data bit, where as the positive edge of SCLK is used to sample incoming serial data.

Discrete I2S Timing

I2S timing uses an LRCLK to define when the data being transmitted is for the left channel and when it is for the

right channel. The LRCLK is LOW for the left channel and HIGH for the right channel. A bit clock running at 64

Fs is used to clock in the data. There is a delay of one bit clock from the time the LRCLK signal changes state to

the first bit of data on the data lines. The data is written MSB first and is valid on the rising edge of bit clock. The

TAS3218 will mask unused trailing data bit positions.

A.

All data are presented in 2's complement form with MSB first.

Figure 5. SAP I2S Format 64 Fs Format

10

Copyright 2008, Texas Instruments Incorporated

Product Folder Link(s): TAS3218

相关PDF资料 |

PDF描述 |

|---|---|

| TAS3218PZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS5000PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5000PFBG4 | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TAS5001PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| TAS3218IPZPR | 功能描述:音频 DSP Dig Audio SoC for multi-channel app RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS3218PZP | 功能描述:音频 DSP Dig Audio SoC for multi-channel app RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS3218PZPR | 功能描述:音频 DSP Dig Audio SoC for multi-channel app RoHS:否 制造商:Texas Instruments 工作电源电压: 电源电流: 工作温度范围: 安装风格: 封装 / 箱体: 封装:Tube |

| TAS-3225A | 制造商:TEW 功能描述: |

| TAS-3225A 44.000KHZ | 制造商:TEW 功能描述: |

发布紧急采购,3分钟左右您将得到回复。